# **GE Fanuc Automation**

Programmable Control Products

# Series Six™ Redundant Processor Unit

User's Manual

GEK-25366C

June, 1990

## WARNINGS, CAUTIONS, AND NOTES AS USED IN THIS PUBLICATION

## WARNING

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

## CAUTION

Caution notices are used where equipment might be damaged if care is not taken.

#### NOTE

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware and software, nor to provide for every possible contingency in connection with installation, operation, and maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc makes no representation or warranty, expressed, implied, or satutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks for products of GE Fanuc Automation North America, Inc.

| Alarm Master | GEnet       | Modelmaster | Series Three | Series 90  |

|--------------|-------------|-------------|--------------|------------|

| CIMPLICITY   | Genius      | ProLoop     | Series Five  | VuMaster   |

| CIMSTAR      | Logicmaster | Series One  | Series Six   | Workmaster |

@Copyright 1990 GE Fanuc Automation North America, Inc. All Rights Reserved.

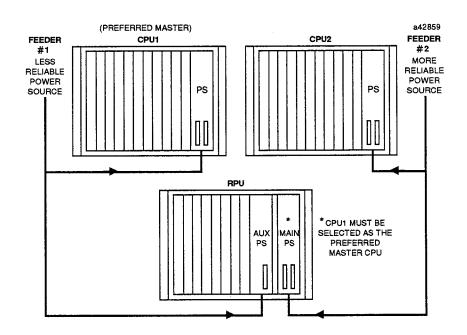

This manual provides information necessary to use a Redundant Processor Unit (RPU) in a Series Six Plus Programmable Controller system. The RPU enhances a Series Six Plus system by acting as a switch to transfer control from one Series Six Central Processor Unit (CPU) to a standby CPU if a failure of the first CPU occurs.

You should become familiar with the capabilities and hardware of the Series Six Plus before attempting to use the RPU. Information on the Series Six hardware can be found in the Series Six Plus User's Manual, GEK-96602, while programming is detailed in the Logicmaster 6 Programming and Documentation Software Manual, GEK-25379.

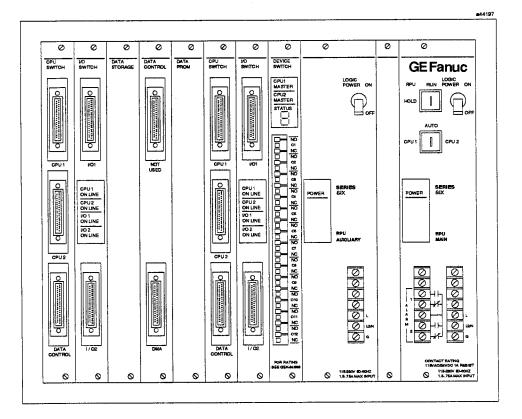

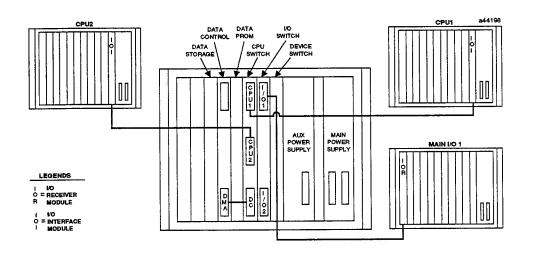

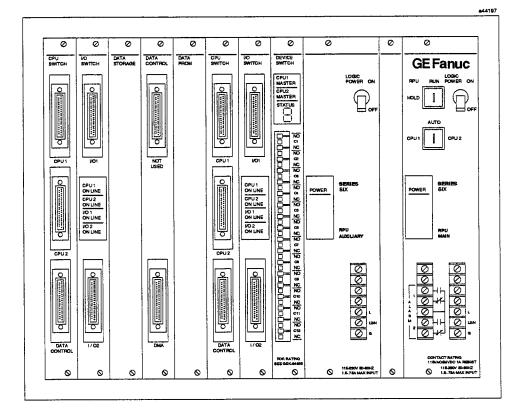

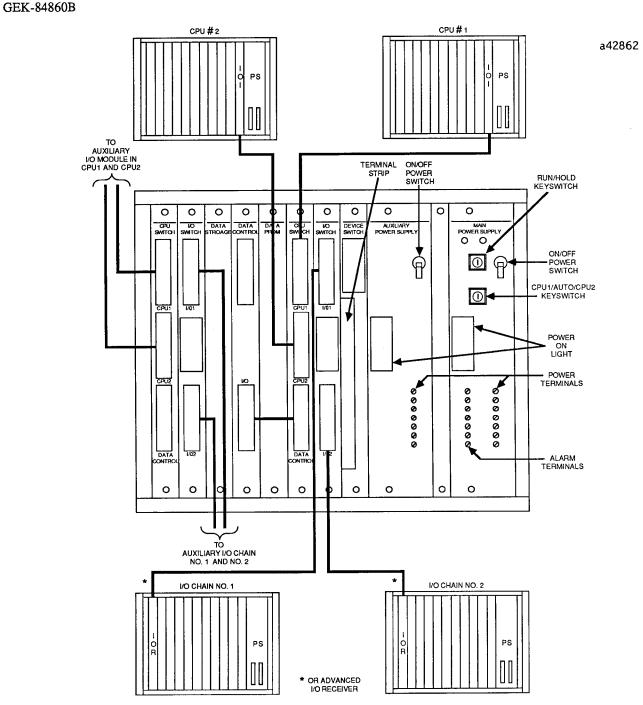

Chapter 1 is a description of the RPU hardware. It includes a general description of the features of the modules used in the RPU. Chapter 2 describes how to install and configure the RPU. A variety of RPU system configurations are shown including systems with Series Six I/O, Genius I/O, and a combination of both types of I/O.

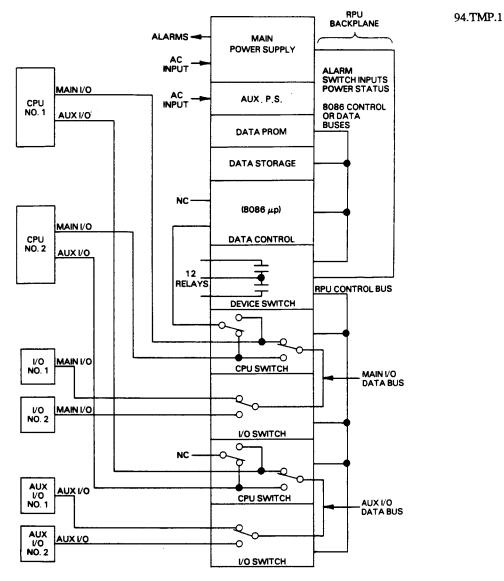

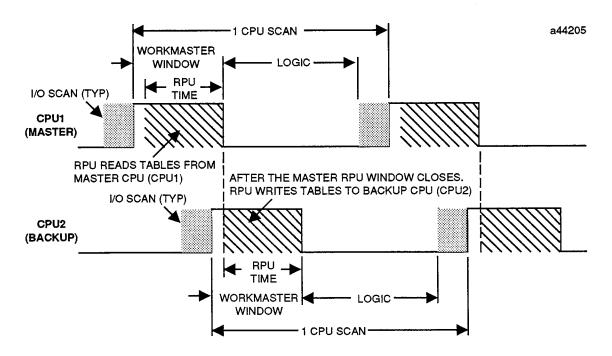

Operator interfaces are discussed in Chapter 3. It includes Light-Emitting Diodes (LED's) and displays as well as alarm relays. Chapter 4 describes the overall function and operation of the RPU. The RPU cycle, RPU/CPU synchronization and the various RPU operating modes are also discussed. Additional information is given concerning the failure transfer sequence, power up sequence, CPU sweep time impact, I/O enable sequence and maximum CPU sweep time.

Chapter 5 provides application information. This includes a description of bumpless transfer and discusses CPU programming as it applies to the RPU. Use of the redundant I/O features, long distance I/O and analog inputs and outputs are covered. This chapter also discusses the Communications Control Module as it pertains to the RPU.

Chapter 6 describes service procedures such as CPU and I/O faults as well as faults which can occur in the RPU.

Following Chapter 6 is a collection of data sheets discussing the RPU and the modules it uses. These data sheets provide further information about the RPU not discussed in the first six chapters.

| CHAPTER | 1. | HARDWARE DESCRIPTION                                 |             |

|---------|----|------------------------------------------------------|-------------|

|         |    | RPU Hardware Description                             | 1-1         |

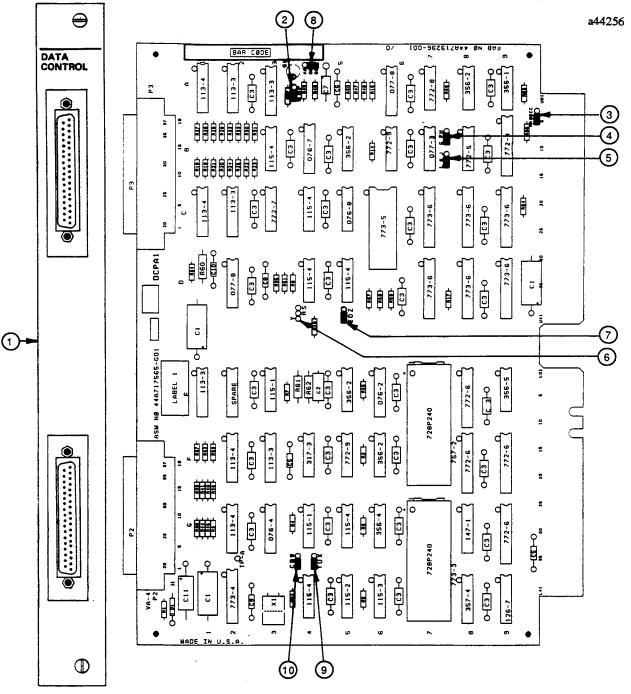

|         |    | Data Control Module                                  | 1-2         |

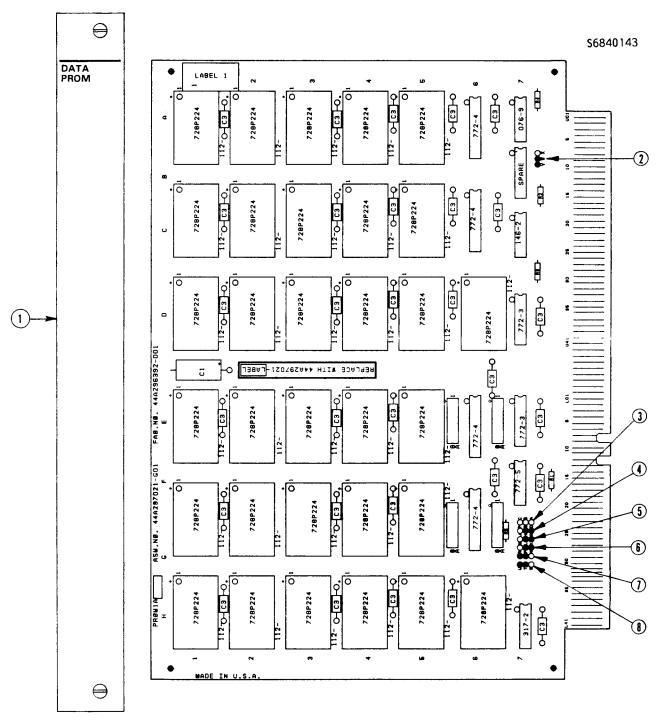

|         |    | Data Prom Module                                     | 1-2         |

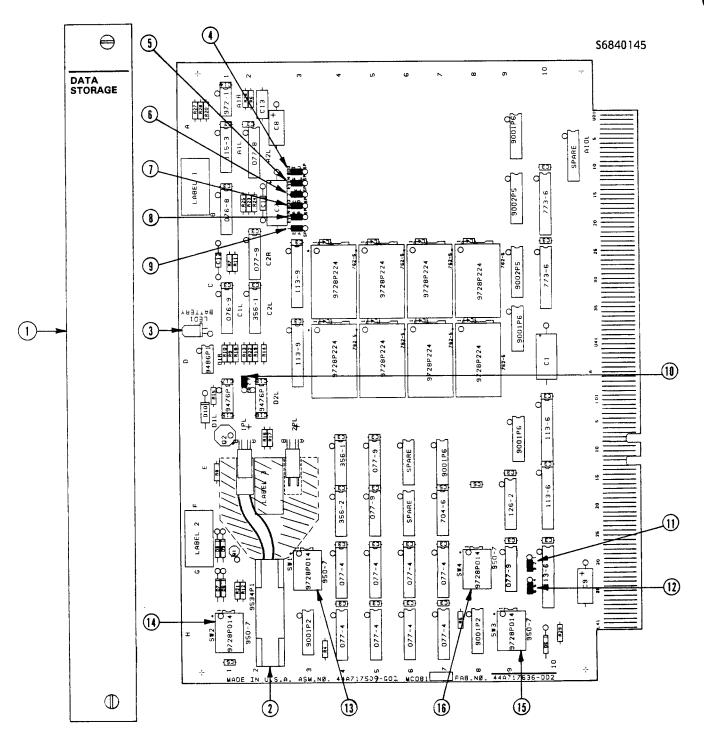

|         |    | Data Storage CMOS Memory Module                      | 1-2         |

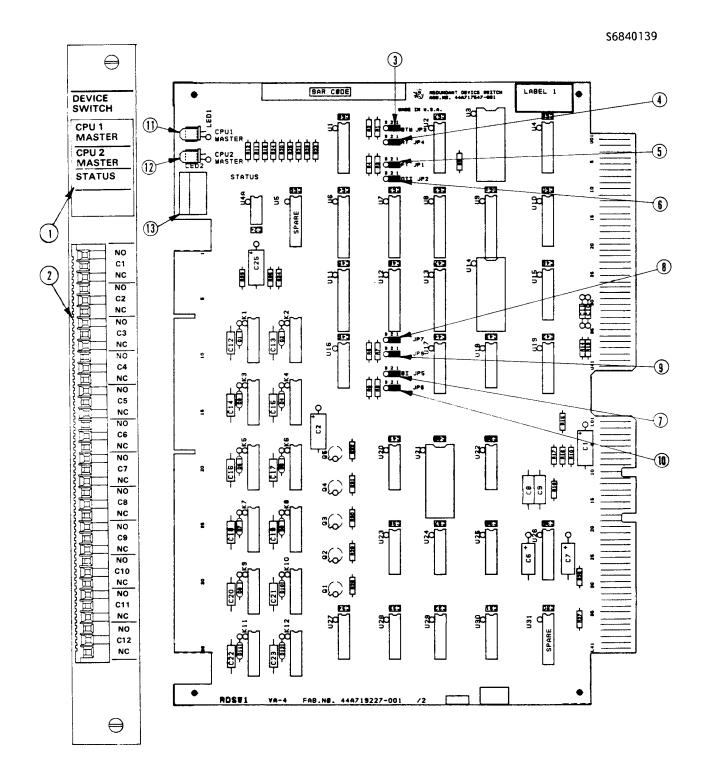

|         |    | Device Switch Module                                 | 1-3         |

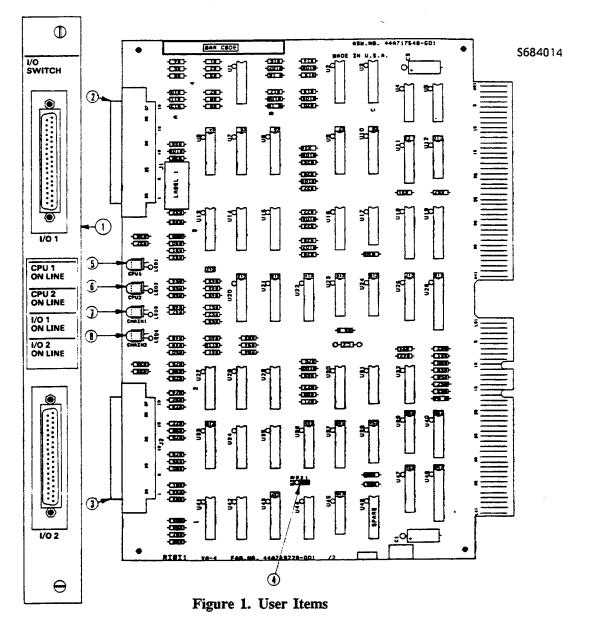

|         |    | CPU Switch Module                                    | 1-3         |

|         |    | I/O Switch Module                                    | 1-3         |

|         |    | Main Power Supply Module                             | 1-3         |

|         |    | Auxiliary Power Supply Module                        | 1-3         |

|         |    | Auxiliary I/O Option (additional CPU and I/O Switch  |             |

|         |    | Modules)                                             | 1-4         |

|         |    |                                                      |             |

| CHAPTER | 2. | INSTALLATION AND CONFIGURATION                       | <b>a</b> 1  |

|         |    | Installation                                         | 2-1         |

|         |    | Power                                                | 2-1         |

|         |    | Grounding                                            | 2-2         |

|         |    | Configuration                                        | 2-2         |

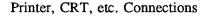

|         |    | I/O Chain Configuration (I/O Switch Module)          | 2-3         |

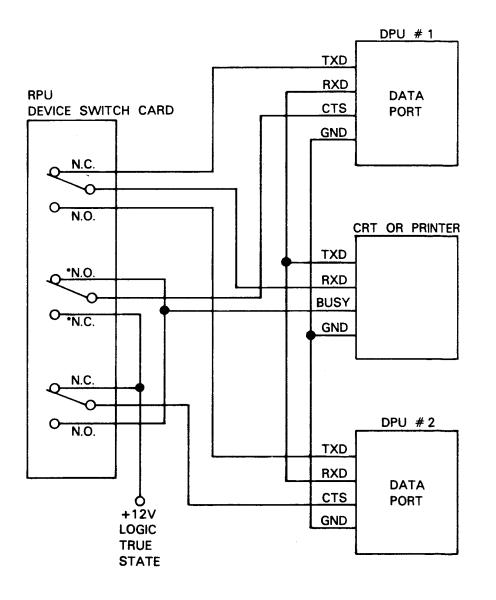

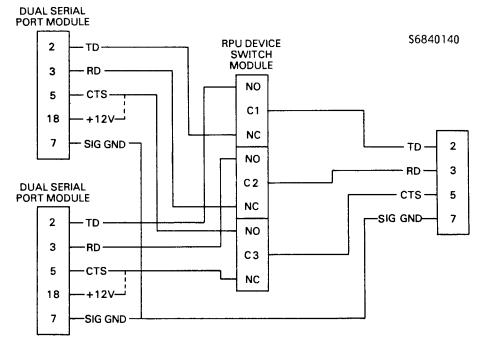

|         |    | Setting Up Data Transfers (Device Switch Module)     | 2-4         |

|         |    | Compatibility Issues                                 | 2-6         |

|         |    | Using Expanded I/O                                   | 2-6         |

|         |    | Transferring Programs from the Workmaster to a CPU   | 2-9         |

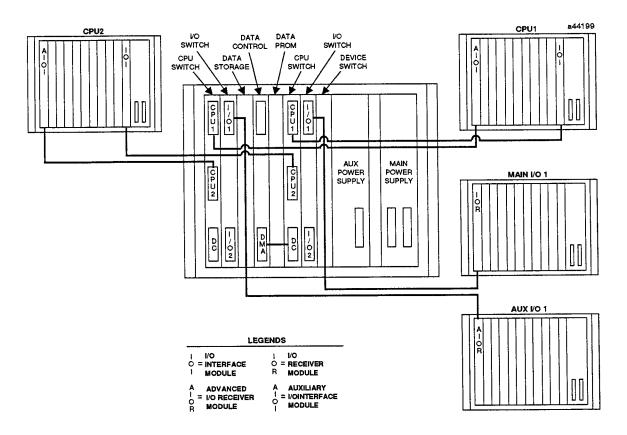

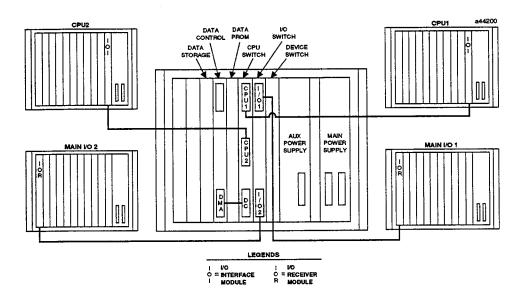

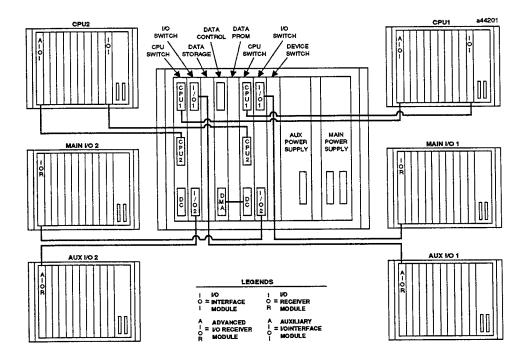

|         |    | Series Six I/O Configurations                        | 2-9         |

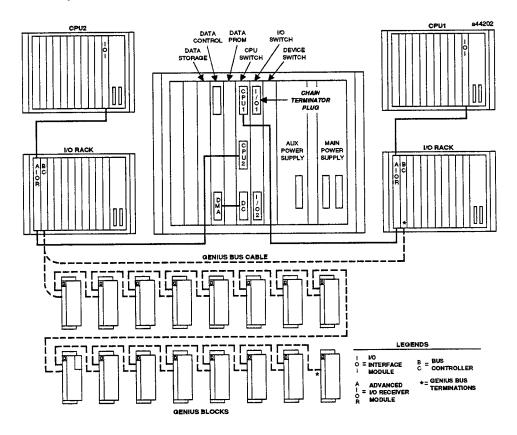

|         |    | Genius I/O Configurations                            | 2-12        |

|         |    | Genius I/O Compatibility with the RPU                | 2-12        |

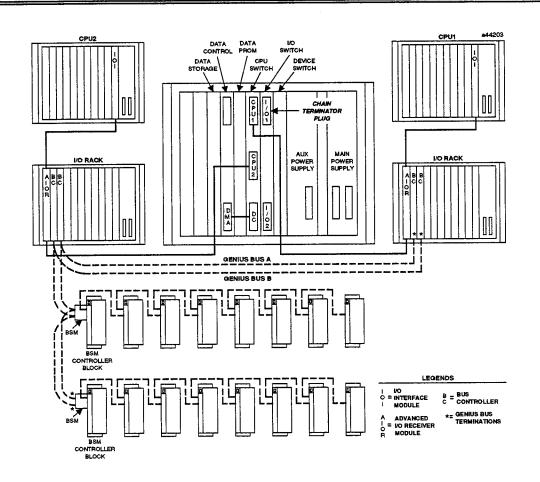

|         |    | Single and Dual Genius I/O Bus Configurations        | 2-13        |

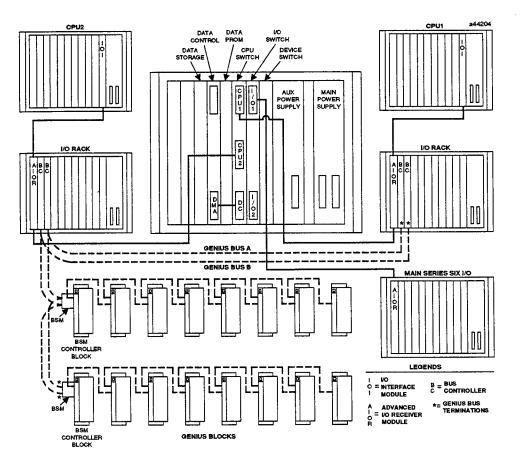

|         |    | Combined Genius I/O and Series Six I/O Configuration | 2-16        |

|         | •  |                                                      |             |

| CHAPTER | 3. | OPERATOR DESCRIPTION                                 | 3-1         |

|         |    | LEDS and Displays                                    | 3-1         |

|         |    | I/O Switch Modules                                   | 3-1         |

|         |    | Device Switch Module                                 | 3-1         |

|         |    | Key Switches                                         |             |

|         |    | CPUI-AUTO-CPU2 Switch                                | 3-2         |

|         |    | RUN-HOLD Switch                                      | 3-2         |

|         |    | Alarm Relays                                         | 3-2         |

|         |    | Device Switch Relays                                 | 3-2         |

| CHAPTER | 4  | RPU OPERATION                                        |             |

|         | •• | Overall Function                                     | 4-1         |

|         |    | RPU Cycle                                            | 4-3         |

|         |    | CPU Window                                           | 4-3         |

|         |    | System Status Check                                  | 4-3         |

|         |    | RPU Self Test                                        | 4-3         |

|         |    | Operations Safeguards                                | 4-4         |

|         |    | RPU - CPU Synchronization                            | 4-4         |

|         |    | •                                                    | 4-5         |

|         |    | RPU Definition of CPU Operating Modes<br>Reset       | 4-5         |

|         |    |                                                      | 4-5         |

|         |    | Self Fault                                           | <b>-</b> -J |

| Content | i |

|---------|---|

|---------|---|

| CHAPTER 4. RPU OPERATION (cont)<br>Direct Memory Access (DMA) Fault 4-5<br>Timed Out 4-5<br>On-Line 4-5<br>Bus-Hung 4-5<br>Backup I/O Parity Error 4-5<br>Backup I/O Parity Error 4-5<br>Failure Transfer Sequence 4-6<br>Switchover Sequence 4-6<br>Restoring the Backup (Backup Initialization) 4-6<br>Hold 4-77<br>Hold-To-Run                                                                  |            |                                         | GEK-25366 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|-----------|

| Direct Memory Access (DMA) Fault 4-5<br>Timed Out 4-5<br>Timed Out 4-5<br>Bus-Hung 4-5<br>Bus-Hung 4-5<br>Backup I/O Parity Error 4-5<br>Backup I/O Parity Error 4-6<br>Restoring the Backup (Backup Initialization) 4-6<br>Power Up Sequence 4-6<br>Hold 4-7<br>Hold-To-Run 4-7<br>CPU Sweep Time Impact 4-7<br>I/O Enable Sequence 4-8<br>Maximum CPU Sweep Time 4-8<br>Maximum CPU Sweep Time 4-8<br>Maximum CPU Sweep Time 5-1<br>Bumpless Transfer of Masters 5-1<br>CPU Programming 5-1<br>Bumpless Transfers 5-2<br>Backup to Master Transfer 5-2<br>Backup to Master Transfer 5-2<br>Backup to Master CPU 5-3<br>CPU Self Fault 5-3<br>Analog Inputs 5-5<br>Analog Inputs 5-5<br>Analog Inputs 5-5<br>Remote I/O 5-7<br>Data Processor (Obsolete) 5-7<br>Communication Control Modules 5-5<br>Remote I/O 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>ASCII BASIC Module Replacement Under Power 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CHAPTER 4. | RPU OPERATION (cont)                    |           |

| Timed Out 4.5<br>On-Line 4.5<br>On-Line 4.5<br>Bus-Hung 4.5<br>Backup I/O Parity Error 4.5<br>Failure Transfer Sequence 4.6<br>Restoring the Backup (Backup Initialization) 4.6<br>Power Up Sequence 4.6<br>Restoring the Backup (Backup Initialization) 4.6<br>Power Up Sequence 4.6<br>Hold 4.7<br>Hold-To-Run 4.7<br>CPU Sweep Time Impact 4.7<br>CPU Sweep Time Impact 4.7<br>CPU Sweep Time Impact 4.7<br>CPU Sweep Time Matters 5.1<br>CPU Programming 5.1<br>Bumpless Transfer of Masters 5.1<br>CPU Programming 5.1<br>Bumpless Transfer of Masters 5.2<br>Backup to Master Transfer 5.2<br>Backup to Master Transfer 5.2<br>Backup to Master Transfer 5.2<br>Backup to Master Transfer 5.2<br>Backup to Master CPU 5.3<br>CPU Self Fault 5.3<br>Dual I/O Chains 5.5<br>Analog Inputs 5.5<br>Analog Inputs 5.5<br>Analog Inputs 5.5<br>Analog Inputs 5.5<br>Analog Inputs 5.5<br>Communication Control Modules 5.5<br>Crite INO Source 1/O<br>Data Processor (Obsolete) 5.7<br>Communication Control Module Type 3 (CCM3) 5.9<br>CCM2 and CCM3 5.9<br>CCM2 and CCM3 5.9<br>CCM2 BASIC Module (and other WINDOW type modules) 5.9<br>ASCII BASIC Module (and other WINDOW type modules) 5.9<br>CHAPTER 6. SERVICE PROCEDURES<br>CPU Faults 6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                         | 4-5       |

| Bus-Hung       4-5         Backup I/O Parity Error       4-5         Backup I/O Parity Error       4-6         Switchover Sequence       4-6         Switchover Sequence       4-6         Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold To-Run       4-7         CPU Sweep Time Impact       4-7         Maximum CPU Sweep Time       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION       5-1         Register Transfers       5-1         CPU Programming       5-1         Register Transfers       5-2         Backup to Master Transfer       5-2         Backup CPU Bit       5-3         Output and Transfer       5-3         Analog I/O with Redundant I/O Systems       5-5         Analog outputs       5-5         Analog outputs       5-5         Communication Control Module       5-9         CCM2 and CCM3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | •                                       | 4-5       |

| Backup I/O Parity Error       4-5         Failure Transfer Sequence       4-6         Switchover Sequence       4-6         Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold-To-Run       4-7         LO Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION         Application Information       5-1         Bumpless Transfer of Masters       5-1         Output and Transition Table Transfers       5-2         Backup to Master Transfer       5-2         Backup CPU Bit       5-2         Determination of Master CPU       5-3         CPU Self Fault       5-3         Dual I/O Chains       5-5         Analog I/O with Redundant I/O Systems       5-5         Analog outputs       5-5         Communication Control Modules       5-9         CCM2 and CCM3       5-9         Communication Control Module Type 3 (CCM3)       5-9         CM2 and CCM3       5-9         CM2 and CCM4       5-1         RPU Faults       6-1         Module Replacement Under Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | On-Line                                 | 4-5       |

| Backup I/O Parity Error       4-5         Failure Transfer Sequence       4-6         Switchover Sequence       4-6         Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold-To-Run       4-7         CPU Sweep Time Impact       4-7         I/O Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION       4-7         Application Information       5-1         Bumpless Transfer of Masters       5-1         Output and Transition Table Transfers       5-2         Backup CPU Bit       5-2         Determination of Master CPU       5-3         CPU Self Fault       5-3         Dual I/O Chains       5-5         Analog Ioputs       5-5         Analog outputs       5-5         Remote I/O       5-7         Cormunication Control Module       5-9         CCM2 and CCM3       5-9         CPU Bit Secor (Obsolete)       5-7         Analog outputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | Bus-Hung                                | 4-5       |

| Failure Transfer Sequence       4-6         Switchover Sequence       4-6         Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold-To-Run       4-7         LO Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION       4-7         Application Information       5-1         Bumpless Transfer of Masters       5-1         CPU Programming       5-1         Register Transfers       5-2         Backup to Master Transfers       5-2         Backup to Master CPU       5-3         CPU Self Fault       5-3         Determination of Master CPU       5-3         Dual I/O Chains       5-5         Analog Inputs       5-5         Analog outputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7         Communication Control Modules       5-9         CCPU and I/O Faults       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CHAPTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                         | 4-5       |

| Switchover Sequence       4-6         Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold-To-Run       4-7         CPU Sweep Time Impact       4-7         I/O Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION         Application Information       5-1         Bumpless Transfer of Masters       5-1         CPU Programming       5-1         Register Transfers       5-2         Backup CPU Bit       5-2         Backup CPU Bit       5-2         Determination of Master CPU       5-3         CPU V Self Fault       5-3         Dual I/O Chains       5-5         Analog I/O with Redundant I/O Systems       5-5         Analog Inputs       5-5         Analog outputs       5-5         COM2 and CCM3       5-9         CCM2 and CCM3       5-9         CPU and I/O Faults       5-9         CPU and I/O Faults       5-1         Maxinu Di I/O Faults       5-9         CPU and I/O Faults       6-1         Module Replacement Under Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                         | 4-6       |

| Restoring the Backup (Backup Initialization)       4-6         Power Up Sequence       4-6         Hold       4-7         Hold-To-Run       4-7         CPU Sweep Time Impact       4-7         I/O Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION       5-1         Bumpless Transfer of Masters       5-1         CPU Programming       5-1         Register Transfers       5-2         Backup CPU Bit       5-3         Output and Transition Table Transfers       5-2         Backup CPU Bit       5-3         CPU Self Fault       5-3         Dual I/O Chains       5-5         Analog I/O with Redundant I/O Systems       5-5         Analog outputs       5-5         Analog outputs       5-5         Communication Control Modules       5-9         CCM2 and CCM3       5-9         CCM2 and I/O Faults       5-9         CCM2 and I/O Faults       5-9         CPU and I/O Faults       6-1         RPU Faults       6-1         Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                         | 4-6       |

| Power Up Sequence4-6Hold4-7Hold To-Run4-7CPU Sweep Time Impact4-7I/O Enable Sequence4-8Maximum CPU Sweep Time4-8CHAPTER 5.APPLICATION INFORMATIONApplication Information5-1Bumpless Transfer of Masters5-1CPU Programming5-1Register Transfers5-1Output and Transition Table Transfers5-2Backup CPU Bit5-2Backup CPU Bit5-3CPU Self Fault5-3Dual I/O Chains5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9Communications Control Module Type 3 (CCM3)5-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURES6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | *                                       | 4-6       |

| Hold4-7Hold-To-Run4-7CPU Sweep Time Impact4-7I/O Enable Sequence4-8Maximum CPU Sweep Time4-8CHAPTER 5.APPLICATION INFORMATIONApplication Information5-1Bumpless Transfer of Masters5-1CPU Programming5-1Register Transfers5-1Output and Transition Table Transfers5-2Backup to Master Transfer5-2Backup to Master Transfer5-2Backup to Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-5Analog Inputs5-5Analog Inputs5-5Analog Inputs5-5Remote I/O5-7Communications Control Modules5-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURES6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                         | 4-6       |

| CPU Sweep Time Impact4-7I/O Enable Sequence4-8Maximum CPU Sweep Time4-8CHAPTER 5.APPLICATION INFORMATIONApplication Information5-1Bumpless Transfer of Masters5-1CPU Programming5-1Register Transfers5-1Output and Transition Table Transfers5-2Backup to Master Transfer5-2Backup CPU Bit5-2Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7CCM2 and CCM35-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURES6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                         | 4-7       |

| I/O Enable Sequence4-8<br>Maximum CPU Sweep Time4-8CHAPTER 5.APPLICATION INFORMATION<br>Application Information5-1<br>Bumpless Transfer of MastersCPU Programming5-1<br>Register TransfersOutput and Transition Table Transfers5-2<br>Backup to Master TransferDutput and Transition Table Transfers5-2<br>Backup to Master TransferDutput and Transition Table Transfers5-2<br>Backup to Master TransferDutput and Transition Table Transfers5-2<br>Backup CPU BitDutput U Bit5-3<br>CPU Self FaultDual I/O Chains5-3<br>Analog InputsAnalog I/O with Redundant I/O Systems5-5<br>Remote I/OAnalog outputs5-5<br>Remote I/ODual Processor (Obsolete)5-7<br>Communication Control ModulesCCM2 and CCM35-9<br>CCM2 and CCM3CCM2 and CCM35-9<br>CCM2 and I/O BusASCII BASIC Module (and other WINDOW type modules)SERVICE PROCEDURES<br>CPU and I/O FaultsCHAPTER 6.SERVICE PROCEDURES<br>CPU and I/O FaultsCHAPTER 6.SERVICE PROCEDURES<br>CPU and I/O FaultsCPU And I/O FaultsGel Nodule Replacement Under Power6-1<br>Module Replacement Under Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | Hold-To-Run                             | 4-7       |

| I/O Enable Sequence       4-8         Maximum CPU Sweep Time       4-8         CHAPTER 5.       APPLICATION INFORMATION       5-1         Application Information       5-1         Bumpless Transfer of Masters       5-1         CPU Programming       5-1         Register Transfers       5-1         Output and Transition Table Transfers       5-2         Backup to Master Transfer       5-2         Backup CPU Bit       5-2         Determination of Master CPU       5-3         CPU Self Fault       5-3         Dual I/O Chains       5-3         Analog Iputs       5-5         Analog Inputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7         CCM2 and CCM3       5-9         CCM2 and CCM3       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CHAPTER 6.       SERVICE PROCEDURES       6-1         RPU Faults       6-1       Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | CPU Sweep Time Impact                   | 4-7       |

| Maximum CPU Sweep Time4-8CHAPTER 5.APPLICATION INFORMATIONApplication Information5-1Bumpless Transfer of Masters5-1CPU Programming5-1Register Transfers5-1Output and Transition Table Transfers5-2Backup to Master Transfer5-2Backup to Master Transfer5-2Backup CPU Bit5-2Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-5Analog I/O with Redundant I/O Systems5-5Analog outputs5-5Remote I/O5-7Cormmunication Control Modules5-9CCM2 and CCM35-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURES6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                         | 4-8       |

| CHAPTER 5.APPLICATION INFORMATIONApplication Information5-1Bumpless Transfer of Masters5-1CPU Programming5-1Register Transfers5-1Output and Transition Table Transfers5-2Backup to Master Transfer5-2Backup CPU Bit5-2Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Module5-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1MOdule Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | A A A A A A A A A A A A A A A A A A A   | 4-8       |

| Application5-1BumplessTransfer of Masters5-1CPUProgramming5-1RegisterTransfers5-1Output and TransitionTable Transfers5-2Backup toMasterTransfer5-2Backup CPU Bit5-35-2Determination of Master CPU5-35-3CPU Self Fault5-35-3Dual I/O Chains5-55-5Analog I/O with Redundant I/O Systems5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURES6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHAPTER 5  | -                                       |           |

| Bumpless Transfer of Masters 5-1<br>CPU Programming 5-1<br>Register Transfers 5-1<br>Output and Transition Table Transfers 5-2<br>Backup to Master Transfer 5-2<br>Backup CPU Bit 5-2<br>Determination of Master CPU 5-3<br>CPU Self Fault 5-3<br>Dual I/O Chains 5-3<br>Analog I/O with Redundant I/O Systems 5-5<br>Analog Inputs 5-5<br>Analog outputs 5-5<br>Remote I/O 5-7<br>Data Processor (Obsolete) 5-7<br>Communication Control Modules 5-9<br>CCM2 and CCM3 5-9<br>CCM2 and CCM3 5-9<br>CCM2 and CCM3 5-9<br>CCM2 Int CCM3 5-9<br>CCM4 Int CCM3 5-9<br>CCM2 Int CCM3 5-9<br>CCM3 5-9<br>CCM2 Int CCM3 5-9<br>CCM3 5- | CHAILER J. |                                         | 5-1       |

| CPU Programming 5-1<br>Register Transfers 5-2<br>Backup to Master Transfer 5-2<br>Backup CPU Bit 5-2<br>Backup CPU Bit 5-2<br>Determination of Master CPU 5-3<br>CPU Self Fault 5-3<br>Dual I/O Chains 5-3<br>Analog I/O with Redundant I/O Systems 5-5<br>Analog Inputs 5-5<br>Analog outputs 5-5<br>Remote I/O 5-7<br>Data Processor (Obsolete) 5-7<br>Communication Control Modules 5-9<br>CCM2 and CCM3 5-9<br>CCM2 and I/O Faults 6-1<br>RPU Faults 6-1<br>Module Replacement Under Power 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                         |           |

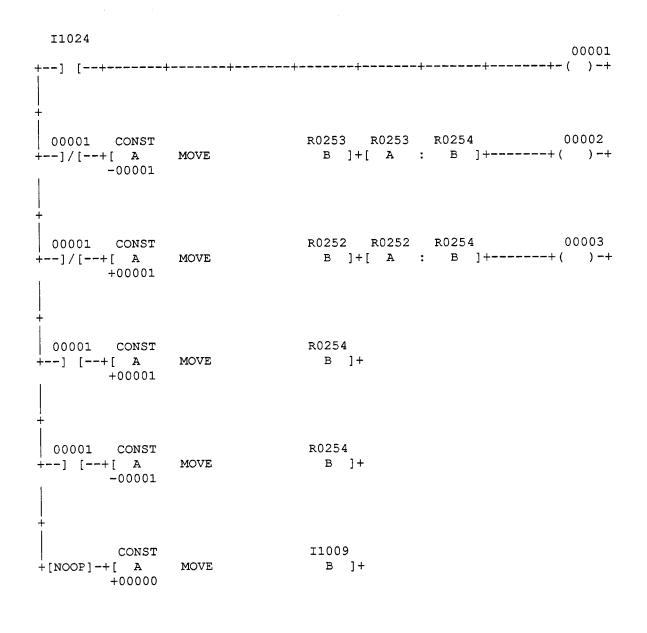

| Register Transfers       5-1         Output and Transition Table Transfers       5-2         Backup to Master Transfer       5-2         Backup CPU Bit       5-2         Determination of Master CPU       5-3         CPU Self Fault       5-3         Dual I/O Chains       5-3         Analog I/O with Redundant I/O Systems       5-5         Analog Inputs       5-5         Analog outputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7         Communication Control Modules       5-9         CCM2 and CCM3       5-9         GENIUS I/O Bus       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CHAPTER 6.       SERVICE PROCEDURES         CPU and I/O Faults       6-1         Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | •                                       |           |

| Output and Transition Table Transfers5-2Backup to Master Transfer5-2Backup CPU Bit5-2Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog outputs5-5Analog outputs5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9Communications Control Module Type 3 (CCM3)5-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                         |           |

| Backup to Master Transfer5-2Backup CPU Bit5-2Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog outputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                         |           |

| Backup CPU Bit5-2Backup CPU Bit5-3Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9COMMUNICATIONS Control Module Type 3 (CCM3)5-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | •                                       |           |

| Determination of Master CPU5-3CPU Self Fault5-3Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Communication Control Modules5-9CCM2 and CCM35-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 1 A A A A A A A A A A A A A A A A A A A |           |

| CPU Self Fault 5-3<br>Dual I/O Chains 5-3<br>Analog I/O with Redundant I/O Systems 5-5<br>Analog Inputs 5-5<br>Analog outputs 5-5<br>Remote I/O 5-7<br>Data Processor (Obsolete) 5-7<br>Cornrunication Control Modules 5-9<br>CCM2 and CCM3 5-9<br>CCM2 and CCM3 5-9<br>GENIUS I/O Bus 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>CPU and I/O Faults 6-1<br>RPU Faults 6-1<br>Module Replacement Under Power 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | ▲                                       |           |

| Dual I/O Chains5-3Analog I/O with Redundant I/O Systems5-5Analog Inputs5-5Analog outputs5-5Remote I/O5-7Data Processor (Obsolete)5-7Cornrnunication Control Modules5-9CCM2 and CCM35-9Communications Control Module Type 3 (CCM3)5-9GENIUS I/O Bus5-9ASCII BASIC Module (and other WINDOW type modules)5-9CHAPTER 6.SERVICE PROCEDURESCPU and I/O Faults6-1RPU Faults6-1Module Replacement Under Power6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                         |           |

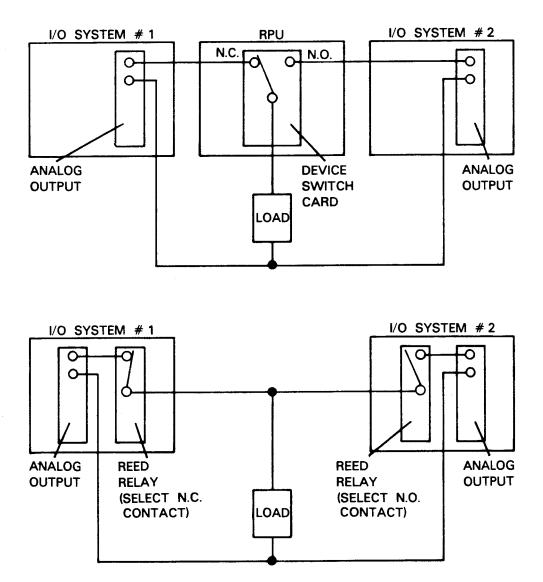

| Analog I/O with Redundant I/O Systems 5-5<br>Analog Inputs 5-5<br>Analog outputs 5-5<br>Remote I/O 5-7<br>Data Processor (Obsolete) 5-7<br>Cornrunication Control Modules 5-9<br>CCM2 and CCM3 5-9<br>COmmunications Control Module Type 3 (CCM3) 5-9<br>GENIUS I/O Bus 5-9<br>ASCII BASIC Module (and other WINDOW type modules) 5-9<br>CPU and I/O Faults 6-1<br>RPU Faults 6-1<br>Module Replacement Under Power 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                         |           |

| Analog Inputs       5-5         Analog outputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7         Communication Control Modules       5-9         CCM2 and CCM3       5-9         Communications Control Module Type 3 (CCM3)       5-9         GENIUS I/O Bus       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CPU and I/O Faults       6-1         RPU Faults       6-1         Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                         |           |

| Analog outputs       5-5         Remote I/O       5-7         Data Processor (Obsolete)       5-7         Communication Control Modules       5-9         CCM2 and CCM3       5-9         Communications Control Module Type 3 (CCM3)       5-9         GENIUS I/O Bus       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CHAPTER 6.       SERVICE PROCEDURES         CPU and I/O Faults       6-1         RPU Faults       6-1         Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | ÷ ·                                     |           |

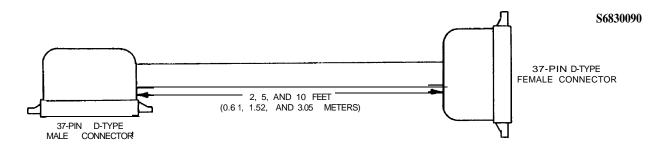

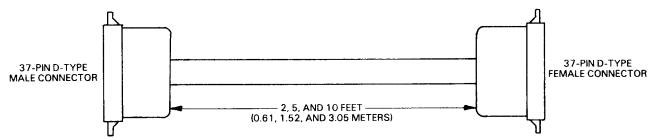

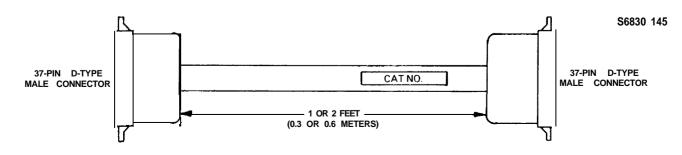

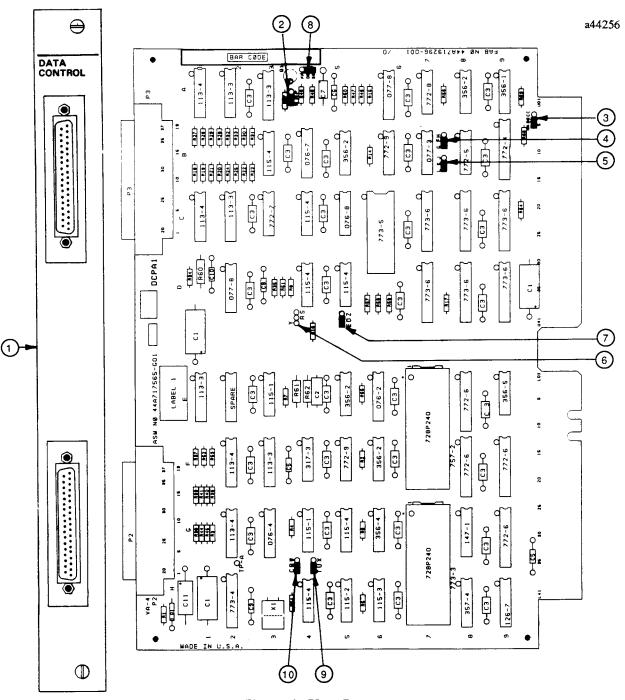

| Remote I/O       5-7         Data Processor (Obsolete)       5-7         Communication Control Modules       5-9         CCM2 and CCM3       5-9         Communications Control Module Type 3 (CCM3)       5-9         GENIUS I/O Bus       5-9         ASCII BASIC Module (and other WINDOW type modules)       5-9         CPU and I/O Faults       6-1         RPU Faults       6-1         Module Replacement Under Power       6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | <b>U</b> 1                              |           |