# **GE Fanuc Automation**

Programmable Control Products

# Series One<sup>tm</sup>/Series Three<sup>tm</sup> Data Communications

User's Manual

GEK-90477A

December, 1986

Copyright 1986 by General Electric Company

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware and software, nor to provide for every possible contingency in connection with installation, operation, and maintenance. Features may be described herein which are not present in all hardware and software systems. General Electric assumes no obligation of notice to holders of this document with respect to changes subsequently made.

General Electric makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the Information contained herein. No warranties of merchantability of fitness for purpose shall apply.

## WARNING, CAUTION, AND NOTES AS USED IN THIS PUBLICATION

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

## CAUTION

Caution notices are used where equipment might be damaged if care is not taken.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

#### NOTE

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

AUTOMATION CONTROLS OPERATIONS, GENERAL ELECTRIC COMPANY, CHARLOTTESVILLE, VIRGINIAPR~~~EU

#### PREFACE

This manual provides information necessary to implement a serial communications link between a Series Six PC or host computer and a Series One, Series One Junior, Series One Plus, or Series Three PC.

You should become familiar with the operation of the Series One, Series One Junior, Series One Plus, or Series Three PCs (depending on your application) before reading this manual. Also, if a Series Six is to be included in your communications link, you may wish to refer to the Series Six Data Communication Manual, GEK-25364, for complete information on Series Six Data Communications.

<u>Chapter 1</u>, Introduction, describes the capabilities of the Data Communications Unit (DCU) and the Data Communications Module (DCM) and possible system configurations of Series One, Series One Junior, Series One Plus, and Series Three PCs with a Series Six PC or host computer.

<u>Chapter 2</u>, Installation and Operation of the Data Communications Unit for the Series One, Series One Junior, and Series One Plus PCs, describes the operation of the Data Communication Unit's user interfaces and the installation of the DCU.

<u>Chapter 3</u>, Installation and Operation of the Data Communications Module for the Series Three PC, describes the operation of the Data Communication Module's user interfaces and the installation of the DCM.

<u>Chapter 4</u>, Electrical Interface Circuits, provides the information needed to construct cables to connect the DCU or DCM to other devices.

<u>Chapter 5</u>, Communication Examples, explains how to build the Series Six ladder diagram to initiate communications between a Series Six PC and a Series One, Series One Junior, Series One Plus, or Series Three PC.

<u>Chapter</u> 6, Serial Interface Protocol, provides complete reference information on DCU and DCM serial interface protocol and timing to allow the user to write a serial communications driver for a host computer or microprocessor.

| CHAPTER 1: | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-1                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|            | Communication Capabilities Using the DCU or DCM                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                                                                                     |

|            | System Configurations <b>Using the DCU or</b> DCM<br>Point-to-Point Configurations<br>Multidrop Configurations                                                                                                                                                                                                                                                                                                                                                                   | 1 - 1<br>1 - 2<br>1 - 3                                                                 |

| CHAPTER 2: | INSTALLATION AND OPERATION OF THE DATA<br>COMMUNICATIONS UNIT FOR THE SERIES ONE<br>FAMILY OF PCS                                                                                                                                                                                                                                                                                                                                                                                | 2-1                                                                                     |

|            | Description and Operation of the User interfaces for the DCU                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 - 1                                                                                   |

|            | LED Indicators<br>Front Panel Connectors<br>Programmer Connector<br>Communications Connector<br>DCU Configuration Switches<br>ON/OFF-LINE Switch<br>CPU (Unit) ID DIP Switches<br>Communication Port Configuration DIP Switches<br>External Power Supply Connector<br>Power Supply Select Switch<br>Using the DCU with CPU Pack Power                                                                                                                                            | 2-2<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>2-6<br>2-7<br>2-7<br>2-7                      |

|            | Installing the DCU                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-9                                                                                     |

|            | Power Cycle Conditions Affecting System Operation                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-10                                                                                    |

| CHAPTER 3: | INSTALLATION AND OPERATION OF THE DATA<br>COMMUNICATIONS MODULE FOR THE SERIES THREE PC                                                                                                                                                                                                                                                                                                                                                                                          | 3-1                                                                                     |

|            | Description and Operation of the DCM's User Interfaces<br>LED Indicators<br>Front Panel Connectors<br>Series Three CPU Connector<br>Communications Connector<br>External Power Supply Connector<br>DCM Configuration Switches<br>ON/OFF-LINE Switch<br>Interaction between the DCM ON/OFF LINE<br>Switch and the CPU Keyswitch<br>CPU (Unit) ID DIP Switches<br>Communication Port Configuration DIP Switches<br>Power Supply Select Switch<br>Using the DCM with CPU Rack Power | 3-1<br>3-2<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-8 |

|            | Installing the DCM                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-10                                                                                    |

|            | Power Cycle Conditions Affecting System Operation                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-11                                                                                    |

| CHAPTER | 4: | ELECTRICAL INTERFACE CIRCUITS AND<br>DIAGNOSTICS FOR THE DCU AND DCM                                                                                                                                                                                                                  | 4-7                                                      |

|---------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|         |    | Port Characteristics                                                                                                                                                                                                                                                                  | 4 - 1                                                    |

|         |    | Communications Port Mating Connector                                                                                                                                                                                                                                                  | 4-2                                                      |

|         |    | Cable Selection                                                                                                                                                                                                                                                                       | 4-2                                                      |

|         |    | Catalog Numbers for GE Supplied Cables                                                                                                                                                                                                                                                | 4-3                                                      |

|         |    | Grounding                                                                                                                                                                                                                                                                             | 4-3                                                      |

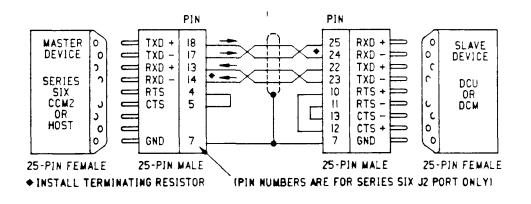

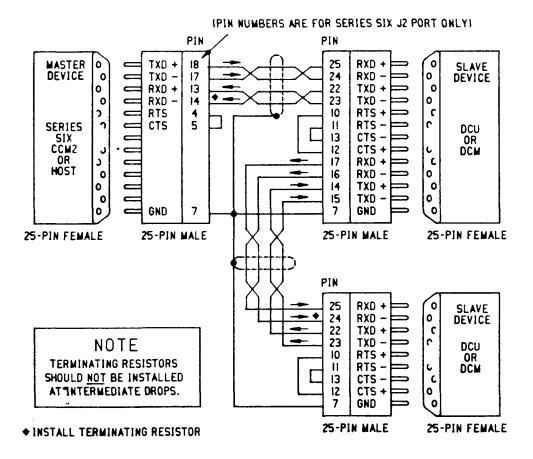

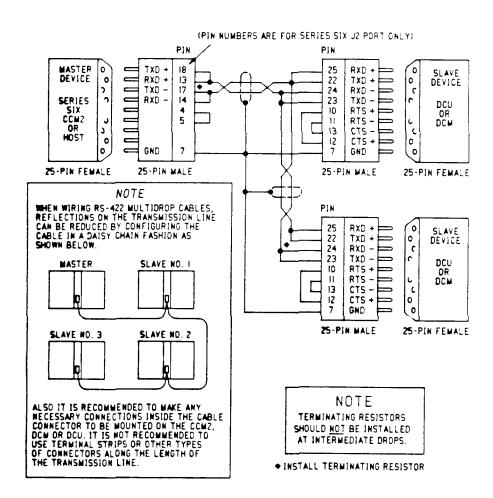

|         |    | RS-422 Direct Cable Diagrams<br>Selection of Terminating Resistors<br>Point-to-Point DCU or DCM to Series Six CCM<br>or Host Computer<br>Multidrop RS-422 Cable, 4-Wire<br>RS-422 Link Connector<br>Multidrop RS-422 Cable, 2-Wire                                                    | 4-3<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7                   |

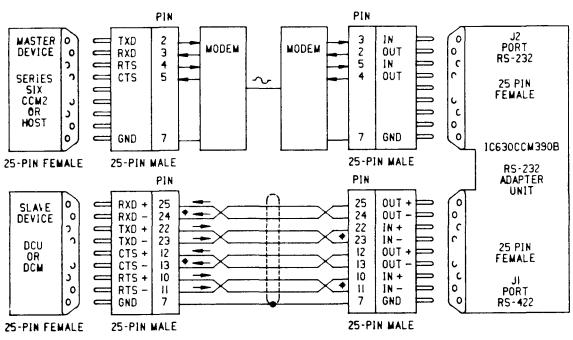

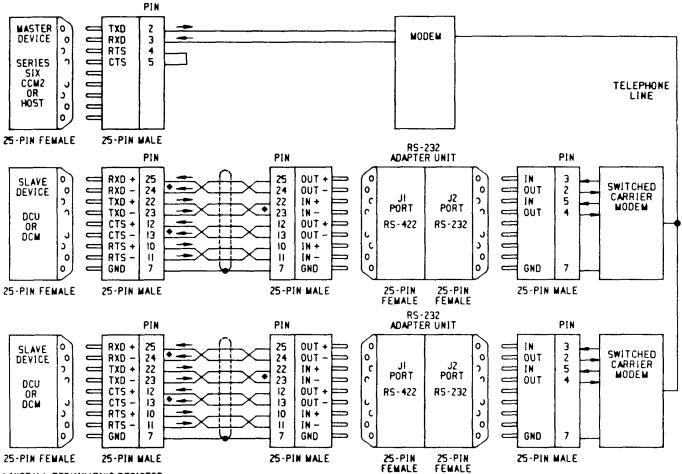

|         |    | Modem Configuration Cable Diagrams<br>Point-to-Point Modem Configuration<br>Cable Diagram<br>Multidrop Modem Configuration Cable Diagram                                                                                                                                              | 4-8<br>4-9<br>4-10                                       |

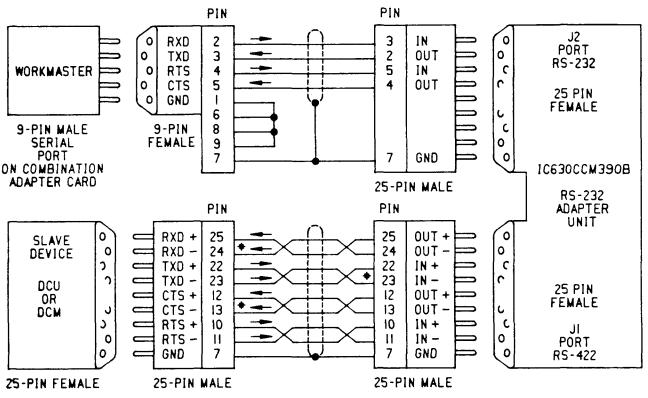

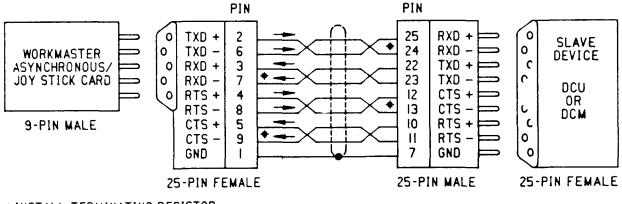

|         |    | DCU or DCM to Workmaster Cable Diagrams<br>DCU or DCM to Workmaster-through the<br>interface Adapter<br>DCU or DCM to Workmaster Directly through<br>the RS-422 Port                                                                                                                  | 4-11<br>4-11<br>4-12                                     |

|         |    | Test Diagnostics<br>Power-Up Diagnostics<br>Loop-Back Diagnostics                                                                                                                                                                                                                     | 4-12<br>4-12<br>4-12                                     |

| CHAPTER | 5: | COMMUNICATION EXAMPLES USING THE<br>SERIES SIX PC AS A MASTER DEVICE                                                                                                                                                                                                                  | 5-1                                                      |

|         |    | Introduction                                                                                                                                                                                                                                                                          | 5-1                                                      |

|         |    | SCREQ Registers<br>Rnnnn: Command Numbers<br>Rnnnn + 1: Target ID<br>Rnnnn + 2: Target Memory Type<br>Rnnnn + 3: Target Memory Address<br>Rnnnn + 4: Data Length<br>Limitations on Amount of Data for the<br>Series One and Series One Junior PCs<br>Rnnnn + 5: Source Memory Address | 5-2<br>5-2<br>5-3<br>5-3<br>5-12<br>5-12<br>5-12<br>5-13 |

-

#### CHAPTER 5: COMMUNICATION EXAMPLES USING THE SERIES SIX PC AS A MASTER DEVICE (Continued)

| Using the Password and Error Checking Features of the<br>Series One Plus PC                                                 | 5-14         |

|-----------------------------------------------------------------------------------------------------------------------------|--------------|

| Logging-In on the Series One Plus CPU<br>Using the Password                                                                 | 5-14         |

| Changing the Password of the Series One Plus PC<br>User Program Error Checking                                              | 5-15<br>5-15 |

| Diagnostic Status Words                                                                                                     | 5-16         |

| Diagnostic Status Word 1 Error Codes<br>Series One, Series One Junior, Series One Plus,<br>and Series Three CPU Error Codes | 5-16<br>5-19 |

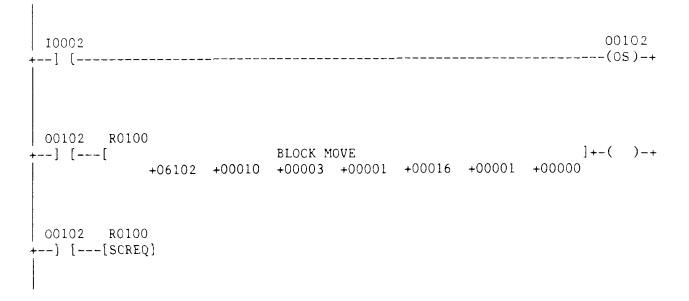

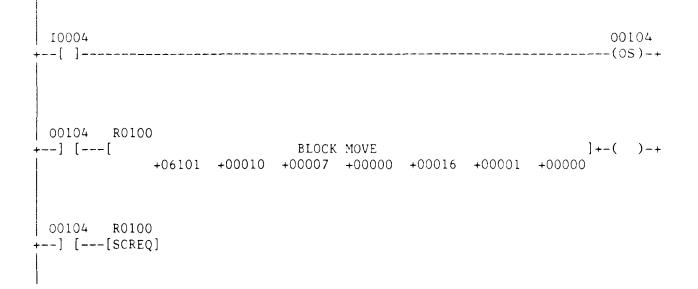

| SCREQ Command Examples                                                                                                      | 5-20         |

| (Sariaa Ona/ Juniar/Dlua)                                                                                                   |              |

| (Series One/Junior/Plus)<br>Example I: Read From Target Timers and Counters                                                 | 5-21         |

| Example 2: Read From Target I/O                                                                                             | 5-22         |

| Example 3: Write to Target I/O                                                                                              | 5-23         |

| (Not Series One Junior)                                                                                                     | 0 20         |

| Example 4: Read From Target User Memory                                                                                     | 5-24         |

| Example 5: Write to Target User Memory                                                                                      | 5-25         |

|                                                                                                                             |              |

| (Series One Plus)                                                                                                           |              |

| Example 6: Read From Target Data Registers                                                                                  | 5-26         |

| Example 7: Write to Target Data Registers                                                                                   | 5-27         |

| Example 8: Write to Target Timer/Counter<br>Accumulators                                                                    | 5-28         |

| Example 9: Logging-In with the Password                                                                                     | 5-30         |

| Example 10: Change Password                                                                                                 | 5-30         |

| Example 10: Change assword<br>Example 11: Check Program Error Code                                                          | 5-32         |

| Example 11. Oneck Hogram Endi Odde                                                                                          | 0-02         |

| (Series Three PC Examples)                                                                                                  |              |

| Example 12: Read from Target Data Registers                                                                                 | 5-35         |

| Example 13: Write to Target Data Registers                                                                                  | 5-36         |

| Example 14: Read from Target Timers and Counters                                                                            | 5-37         |

| Example 15: Write to Target Timer/Counter<br>Accumulators                                                                   | 5-38         |

| Example 16: Read from Target I/O                                                                                            | 5-40         |

| Example 17: Write to Target I/O                                                                                             | 5-41         |

| Example 18: Read from Target User Memory                                                                                    | 5-42         |

| Example 19: Write to Target user Memory                                                                                     | 5-43         |

|                                                                                                                             |              |

| (Series One/Junior/Plus Or Series Three PC Examples)                                                                        | o 11         |

| Example 20: Read PC Type<br>Example 21: Read Target Run/Program Mode                                                        | s-44<br>5-45 |

| Example 21: Read Target Run/Program Mode<br>Example 22: Command Target Run/Program Mode                                     | 5-45<br>5-46 |

| Example 22: Read Target Diagnostic Status Words                                                                             | 5-48         |

| Example 24: Clear Target Diagnostic Status Words                                                                            | 5-40         |

|                                                                                                                             |              |

۰

## CHAPTER 6: SERIAL INTERFACE PROTOCOL

| Introduction, Master-Slave Protocol                | 6 - 1 |

|----------------------------------------------------|-------|

| Asynchronous Data Format                           | 6 - 1 |

| Control Character Coding                           | 6-2   |

| Enquiry Response Delay                             | 6-2   |

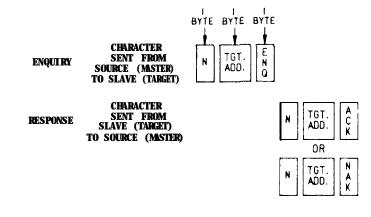

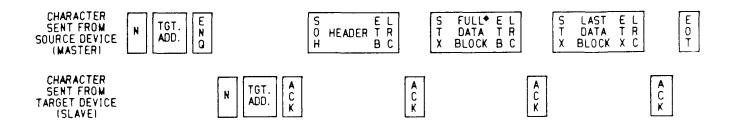

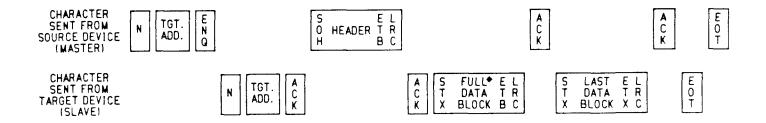

| Normal Sequence*, Master-Slave                     | 6-3   |

| Normal Enquiry Sequence                            | 6-3   |

| Normal Sequence Protocol Format                    | 6-3   |

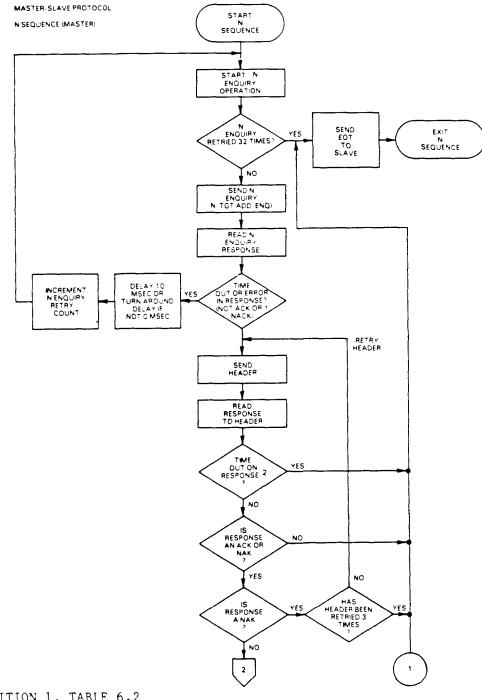

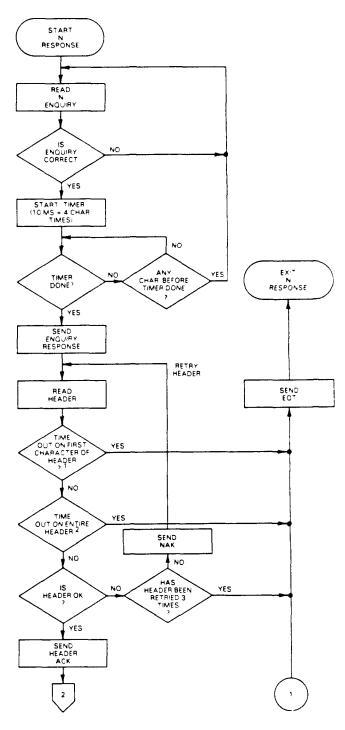

| Master-Slave Normal Sequence Flow Charts           | 6-5   |

| Normal Sequence, Master                            | 6-5   |

| Normal Response, Slave                             | 6-5   |

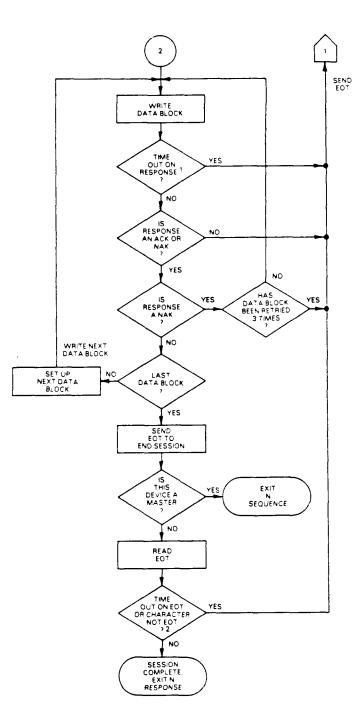

| Write Data Blocks, Master or Slave                 | 6-10  |

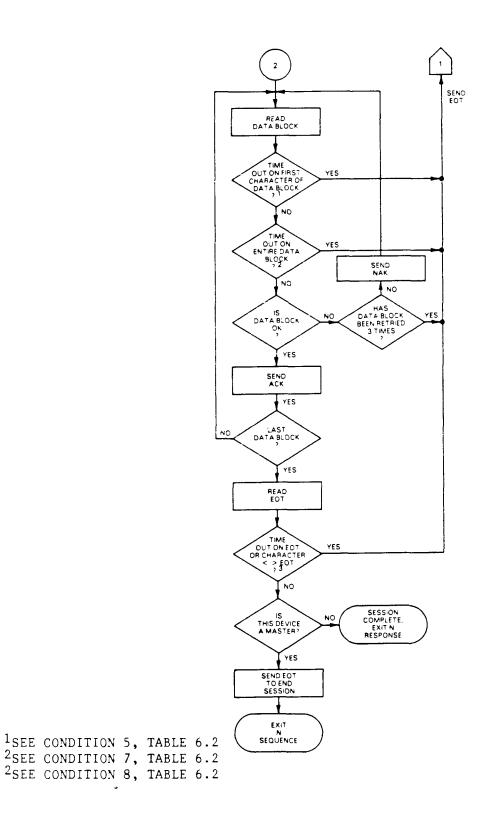

| Read Data Blocks, Master or Slave                  | 6-10  |

| Master-Slave Message Transfers                     | 6-11  |

| Header Block                                       | 6-11  |

| DCU or DCM ID Number                               | 6-12  |

| Data Flow Direction and Memory Type                | 6-12  |

| Target Memory Address                              | 6-12  |

| Number of Complete Data Blocks<br>to Follow Header | 6-14  |

| Number of Bytes in Incomplete Last Block           | 6-14  |

| Source ID Number                                   | 6-14  |

| Text Data Block                                    | 6-15  |

| Header and Text Data Block Response                | 6-16  |

| Message Termination                                | 6-16  |

| Timing Considerations                              | 6-16  |

| Serial Link Time-Outs                              | 6-16  |

| Turn-Around Delays                                 | 6-16  |

| Communication Errors                               | 6-18  |

| Invalid Header                                     | 6-18  |

| Invalid Data                                       | 6-19  |

| Invalid NAK, ACK, or EOT                           | 6-19  |

| Serial Link Time Out                               | 6-19  |

| Accessing the CPU Scratch-Pad                      | 6-19  |

| Using the Password and Error Checking Features of  | 6-20  |

| the Series One Plus PC                             |       |

| Logging-In on the Series One Plus CPU              | 6-20  |

| Using the Password                                 |       |

| Changing the Password of the                       | 6-21  |

| Series One Plus PC                                 |       |

| User Program Error Checking                        | 6-21  |

#### TABLES

| Number | Description                                                                                           | Page |

|--------|-------------------------------------------------------------------------------------------------------|------|

| 2.1    | Communications Port Configuration Dip-Switch Settings                                                 | 2-6  |

| 2.2    | Series One Units of Load (Supplied)                                                                   | 2-7  |

| 2.3    | Series One Units of Load (Used)                                                                       | 2-8  |

| 2.4    | Power Cycle Conditions Affecting System Operation<br>(The user program is assumed to be in CMOS RAM.) | 2-10 |

| 3.1    | Communications Port Configuration Dip-Switch Settings                                                 | 3-7  |

| 3.2    | Series Three Units of Load (Supplied)                                                                 | 3-8  |

| 3.3    | Series Three Units of Load (Used)                                                                     | 3-9  |

| 3.4    | Power Cycle Conditions Affecting System Operation<br>(The user program is assumed to be in CMOS RAM)  | 3-11 |

| 5.1    | Mapping of Series One References to Target Addresses                                                  | 5-5  |

| 5.2    | Mapping of Series One JR References to Target Addresses                                               | 5-6  |

| 5.3    | Mapping of Series One Plus References to Target<br>Addresses                                          | 5-7  |

| 5.4    | Mapping of Series Three References to Target Addresses                                                | 5-9  |

| 5.5    | Unit Lengths of Source and Target Memory Types                                                        | 5-12 |

| 5.6    | Maximum Amount of Data for Series One and<br>Series One Junior Memory Types 1, 3, and 7               | 5-13 |

| 5.7    | Source Memory Address                                                                                 | 5-13 |

| 5.8    | Series One Plus CPU Scratch-Pad Addresses                                                             | 5-14 |

| 5.9    | Diagnostic Status Word Error Codes                                                                    | 5-17 |

| 5.10   | Series One, Series One Junior, Series One Plus,<br>Series Three CPU Error Codes                       | 5-19 |

| 6.1    | Control Character Codes                                                                               | 6-2  |

| 6.2    | Serial Link Time-Outs                                                                                 | 6-17 |

| 6.3    | Series One Plus CPU Scratch-Pad Addresses                                                             | 6-20 |

## FIGURES

| Number | Description                                                                | Page  |

|--------|----------------------------------------------------------------------------|-------|

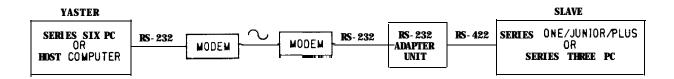

| 1.1    | Point-To-Point Configuration (Direct)                                      | 1 - 2 |

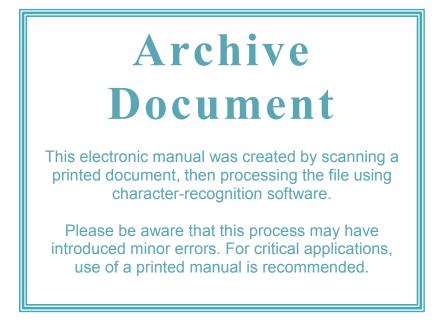

| 1.2    | Point-To-Point Configuration (Using Modems)                                | 1 - 2 |

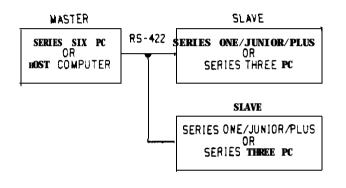

| 1.3    | Multidrop Configuration (Direct)                                           | 1 - 3 |

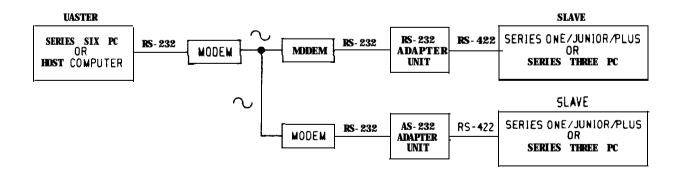

| 1.4    | Multidrop Configuration (Using Modems)                                     | 1 - 3 |

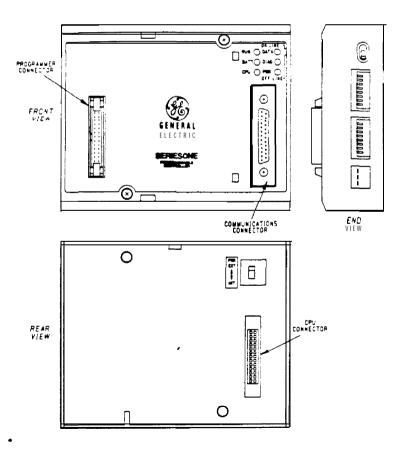

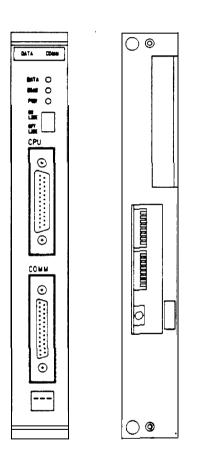

| 2.1    | Front, End, and Rear View of the DCU                                       | 2-1   |

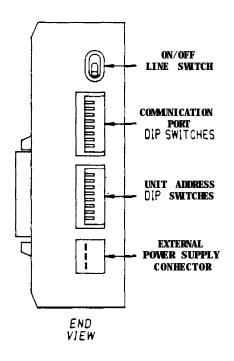

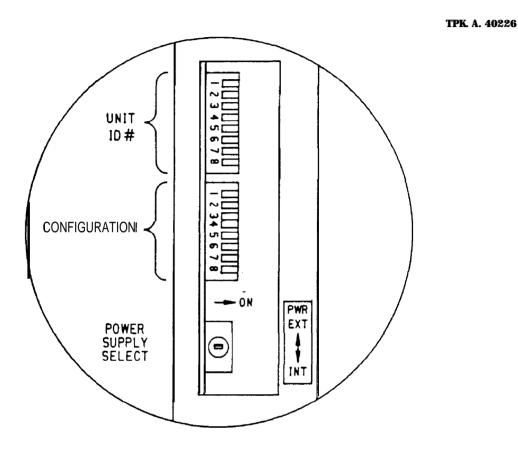

| 2.2    | Location of the DCU Configuration Switches                                 | 2-4   |

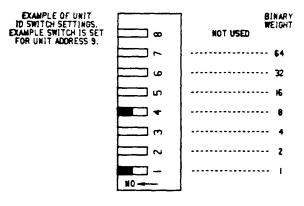

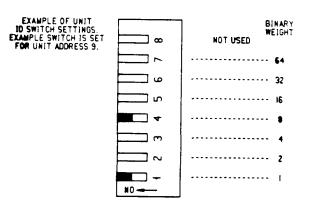

| 2.3    | Dip-Switch Settings for CPU ID Selection                                   | 2-5   |

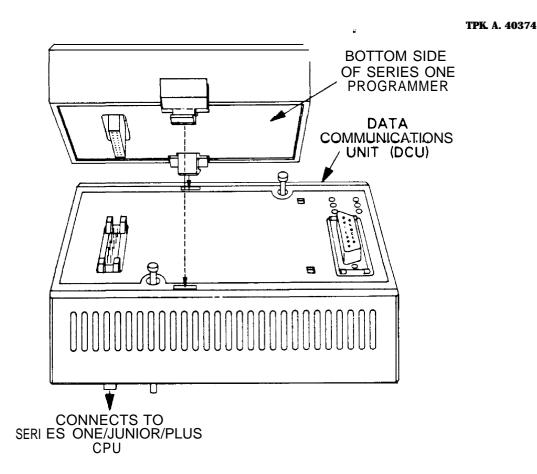

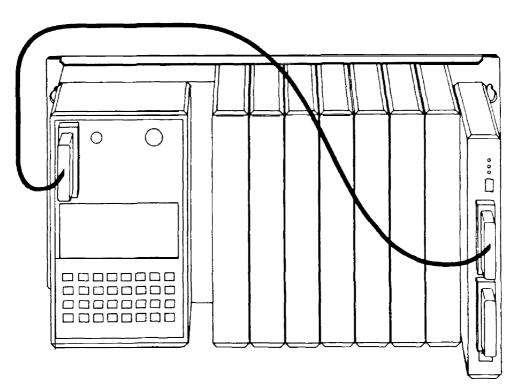

| 2.4    | Connecting the Programmer, DCU, and CPU                                    | 2-9   |

| 3.1    | Front and Rear View of the DCM                                             | 3-1   |

| 3.2    | Location of the DCM Configuration Switches                                 | 3-4   |

| 3.3    | Dip-Switch Settings for CPU ID Selection                                   | 3-6   |

| 3.4    | Connecting the DCM to the CPU                                              | 3-10  |

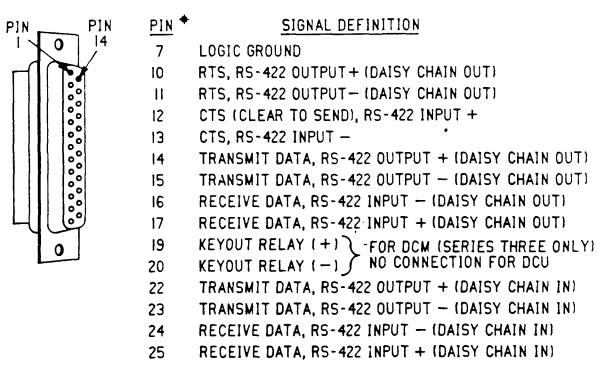

| 4.1    | Communications Connector Pin Assignments                                   | 4 - 1 |

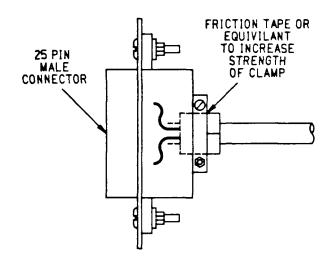

| 4.2    | Assembly of Mating Connector                                               | 4-2   |

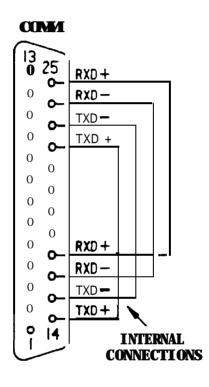

| 4.3    | Link Connector used when a DCU or DCM is removed<br>from a Multidrop Chain | 4-6   |

| 4.4    | Loop-Back Test Connector                                                   | 4-13  |

| 6.1    | Serial Data Format                                                         | 6-1   |

| 6.2    | Data Transfer from Master to Slave                                         | 6-4   |

| 6.3    | Data Transfer from Slave to Master                                         | 6-4   |

| 6.4    | N Sequence, Master                                                         | 6-6   |

| 6.5    | N Response, Slave                                                          | 6-7   |

| 6.6    | Write Data Blocks, Master or Stave                                         | 6-8   |

| 6-7    | Read Data Blocks, Master or Slave                                          | 6-9   |

| 6-8    | Serial Header Format                                                       | 6-11  |

#### CHAPTER 1 INTRODUCTION

The serial interface to the Series One family of PCs is essentially the same as the interface to the Series Three PC. For this reason the user information for both have been combined into one manual. The differences are primarily related to the physical package which affects the installation of the interface. To differentiate between the two interfaces, the terms below are used throughout this manual.

| Data Communications Unit (DCU) -   | Series One, Series One Junior,   |

|------------------------------------|----------------------------------|

|                                    | and Series One Plus PC Interface |

| Data Communications Module (DCM) - | Series Three PC Interface        |

This chapter describes the capabilities and system configurations for serial communications with the Series One Family of programmable controllers and Series Three programmable controllers.

#### COMMUNICATIONS CAPABILITIES USING THE DCU OR DCM

The DCU and DCM provide a serial, RS-422 interface between a Series One, Series One Junior, Series One Plus, or Series Three PC and a device such as a Series Six PC, Workmaster computer or other host computer. Memory types that can be accessed through the DCU or DCM include:

- Discrete input and output points,

- Timer and counter accumulator references (and Series One Plus PC and Series Three PC data registers),

- Scratchpad (including using the password and the user logic error checking capability for the Series One Plus PC),

- User logic, and

- Diagnostic information.

Using the CCM2 protocol, the host computer or Series Six PC can have supervisory control over one or more PCs of the Series One family or one or more Series Three PCs. The data transfer rates as well as other communications parameters for the DCU and DCM are DIP-switch selectable. The primary data transfer rate for direct connections is 19.2 kBps. Other data transfer rates are provided for special purpose interfaces which include modem configurations.

#### SYSTEM CONFIGURATIONS USING THE DCU OR DCM

A system configuration refers to the way in which various devices are combined to form a communications network. As explained below, both point-to-point and multidrop configurations are possible through the DCU or DCM. For details on constructing cables, see Chapter 4, Electrical interface Circuits.

In all configurations, the Series One, Series One Junior, Series One Plus, or Series Three PC is the slave device, and the host computer, Workmaster, or Series Six PC is the master device. A slave can respond only to requests from a master.

When a Workmaster computer or other host computer is the master device, host software must be written to handle the protocol requirements as explained in Chapter 6, Serial Interface Protocol.

#### POINT-TO-POINT CONFIGURATIONS

In the point-to-point configuration, only two elements can be connected to the same communication line. The communication line can be connected directly using the RS-422 electrical interface capability (4000 feet, 1200 meters, maximum), or connected through modems and an RS-232 to RS-422 adapter unit for longer distances over telephone lines.

**TPK.** A. 40369

Figure 1.1 POINT-TO-POINT CONFIGURATION (DIRECT)

**TPK.** A. 40370

Figure 1.2 POINT-TO-POINT CONFIGURATION (USING MODEMS)

#### MULTIDROP CONFIGURATIONS

This configuration permits the connection of a host computer or Series Six PC to a group of Series One, Series One Junior, Series One Plus, or Series Three PCs. As with point-to-point connections, either RS-422 capability or modems can be used. A maximum of 8 slaves can be connected using RS-422. The maximum distance between the two end devices in the multidrop is 4000 feet (1200 meters).

When RS-232 modems are used, an RS-232 adapter unit must be included to convert RS-422 signals from the DCU or DCM to RS-232 signals for the modems.

#### **TPK.** A. 40371

Figure 1.3 MULTIDROP CONFIGURATION (DIRECT)

**TPK.** A. 40372

\*Up to 8 slave devices can be multidropped from the RS-232 Adapter Unit.

Figure 1.4 MULTIDROP CONFIGURATION (USING MODEMS)

#### CHAPTER 2 INSTALLATION AND OPERATION OF THE DATA COMMUNICATIONS UNIT FOR THE SERIES ONE FAMILY OF PCS

This chapter describes the operation of the user interfaces (LEDs, switches, and ports) and the installation of the Data Communications U n it (DCU) (IC610CCM100A, IC610CCM105A).

#### NOTE TO SERIES ONE PLUS USERS

Use only the Data Communications Unit (IC610CCM105A) for communications with the Series One Plus PC.

#### DESCRIPTION AND OPERATION OF THE USER INTERFACES FOR THE DCU

The various indicator lights, connectors, and configuration DIP switches for the DCU are shown in Figure 2.1.

#### TPA. C. 40221

Figure 2.1 FRONT, END, AND REAR VIEW OF THE DCU

#### LED INDICATORS

The six status LED's on the front of the DCU convey the following information:

| <u>Status LED</u> | State_ | Description                                                                                                                                                                                                                              |

|-------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA              | On     | Data being transferred to and from the communication port.                                                                                                                                                                               |

|                   | Off    | Data not being transferred to and from the communication port or data incorrect due to:                                                                                                                                                  |

|                   |        | <ol> <li>Parity overrun or framing errors;</li> <li>Invalid header, data block, control<br/>character, or checksum;</li> <li>Time out on serial link. (Refer to<br/>Chapter 6 for more information on the<br/>protocol used).</li> </ol> |

| DIAG              | On     | Power-up hardware diagnostics have passed.                                                                                                                                                                                               |

|                   | Off    | Power-up hardware diagnostics have failed.                                                                                                                                                                                               |

| PWR               | on     | 5 V dc power to DCU is connected.                                                                                                                                                                                                        |

|                   | Off    | 5 V dc power to DCU is not connected.                                                                                                                                                                                                    |

#### NOTE

Power to the DCU can be supplied from the rack power supply or an external supply. When the power supply select switch is in the EXT position, power must be supplied through the external power supply connector on the side of the DCU. See Figures 2.1 and 2.2.

| <u>Status LED</u> | State | Description                                                                        |

|-------------------|-------|------------------------------------------------------------------------------------|

| RUN               | On    | The CPU is in the RUN mode.                                                        |

|                   | Off   | The CPU is not in the RUN mode.                                                    |

| BATT              | 0 n   | The battery which provides memory back-up in the CPU is not OK.                    |

|                   | off   | The battery which provides memory back-up in the CPU is OK.                        |

| CPU               | On    | There is an error; check the error code on<br>the programmmer display and take the |

|                   | Off   | appropriate action.<br>There is no CPU error.                                      |

#### FRONT PANEL CONNECTORS

Two connectors on the front of the DCU provide an interface to:

- 1. Programmer (Programmer Connector),

- 2. External serial device (Communications Connector).

#### Programmer Connector

The programmer connector is the mating connector which mates with the programmer and connects with the CPU. This permits use of the programmer while the DCU is connected to the CPU. See Figures 2.1 and 2.4.

#### Communications Connector

The communications connector (25-pin female, D-type) provides a serial interface to external devices. A pin-by-pin description of this connector is shown in Chapter 4.

#### DCU CONFIGURATION SWITCHES

The configuration switches are located on the right side of the DCU as shown below.

**TPK.** A. 40373

#### Figure 2.2 LOCATION OF THE DCU CONFIGURATION SWITCHES

#### ON/OFF-LINE Switch

The ON/OFF-LINE switch, which is directly above the DIP switches on the right side of the DCU, enables or disables serial communications with the Series One, Series One Junior, or Series One Plus CPU.

- OFF LINE: Serial communication between the DCU and the CPU is disabled and the CPU is under control of the attached programmmer.

- ON LINE: Serial communication between the DCU and CPU is enabled and the programmer is disabled if attached.

#### CPU (Unit) ID DIP Switches

.

The bottom group of eight DIP switches located on the right side of the DCU determines the CPU ID of 1-90. The switch configuration associated with each ID is shown in Figure 2.3.

TPA.A.40223

| UNIT | T        |   |     | SWI | T        | ЭН |    |          | UNIT |   | 21       | , ; | SWI I | T       | ЭН |   |         | UNIT | T | 51I | P  | SW) | T   | CH |   |          |

|------|----------|---|-----|-----|----------|----|----|----------|------|---|----------|-----|-------|---------|----|---|---------|------|---|-----|----|-----|-----|----|---|----------|

| ID   |          | P | os: | ITI | 101      |    |    |          | ID   |   | PO       | )SI | tT1   | 01      | £  |   |         | ID   |   | P   | 05 | IT: | [0] | 1  |   |          |

|      | 8        | 7 | 6   | 5   | 4        | 3  | 2  | 1        |      | B | 7        | 6   | 5     | 4       | 3  | 2 | 1       |      | 8 | 1   | 6  | 5   | 4   | 3  | 2 | 1        |

| 1    | 1        |   |     |     |          |    | -  | X        | 31   | Γ |          |     |       | X       | X  | X | X       | 61   | Γ |     | X  | X   | X   | X  |   | X        |

| 2    |          |   |     |     |          |    | X  |          | 32   | Γ |          | X   |       |         |    |   |         | 62   | Ι |     | X  | X   | X   | X  | X |          |

| 3    | 1-       |   |     |     |          | -  | X  | X        | 33   | 1 |          | X   |       | _       |    |   | X       | 63   | 1 |     | X  | X   | X   | X  | X | X        |

| 4    | 1        |   |     |     |          | x  |    |          | 34   | - |          | X   |       |         |    | X |         | 64   | Γ | X   | Γ  |     |     |    |   |          |

| 5    | 1        |   |     |     | Г        | I  | -  | X        | 35   | 1 |          | X   |       | -       |    | X | X       | 65   |   | X   | Γ  |     |     |    |   | X        |

| 6    | 1        |   |     |     |          | x  | x  |          | 36   | 1 |          | X   | 1     |         | X  |   |         | 66   |   | X   | Γ  |     |     |    | X |          |

| 7    | 1        |   |     |     |          | X  | X  | X        | 37   | Γ |          | X   | Γ     |         | I  |   | X       | 67   | Г | X   | Γ  |     |     |    | X | X        |

| 8    |          |   |     |     | I        |    | 1  |          | 38   |   | -        | x   |       | Γ       | X  | X |         | 68   | Τ | X   | Γ  |     |     | X  |   |          |

| 9    | T        |   |     |     | X        | 1  | Γ  | X        | 39   | Γ | <u> </u> | X   |       | <b></b> | I  | X | X       | 69   | Γ | X   | Γ  |     |     | I  |   | X        |

| 10   | 1        |   |     |     | X        |    | x  |          | 40   | Т |          | X   | 1     | x       |    |   | <b></b> | 70   | Г | X   | Γ  |     |     | X  | X |          |

| 11   |          |   |     |     | I        | Γ  | X  | X        | 41   |   |          | X   |       | x       |    |   | X       | 71   | Γ | X   | Γ  |     |     | I  | X | X        |

| 12   | 1        |   |     |     | I        | X  | 1  |          | 42   | T | -        | X   | Ī     | X       |    | I |         | 72   | Г | X   | 1  |     | X   | Γ  |   |          |

| 13   | 1        |   |     |     | X        | X  | 1  | X        | 43   | T |          | X   |       | X       |    | X | I       | 73   | Γ | X   | Γ  |     | X   |    |   | X        |

| 14   |          |   |     |     | X        | X  | X  |          | 44   | 1 |          | X   |       | X       | X  |   |         | 74   |   | X   | Γ  |     | X   |    | X |          |

| 15   | Γ        |   |     |     | X        | X  | X  | X        | 45   |   |          | X   |       | X       | X  |   | X       | 75   |   | X   |    |     | X   |    | X | X        |

| 16   | Γ        |   |     | X   |          |    |    |          | 46   |   |          | X   | Γ     | X       | X  | X |         | 76   | Ι | X   | 1  |     | X   | I  |   |          |

| 17   |          |   |     | X   |          |    | Γ  | X        | 47   | Ι |          | I   | Γ     | X       | X  | X | X       | 77   |   | X   | Γ  |     | X   | X  |   | X        |

| 18   | Γ        |   |     | X   |          |    | X  |          | 48   | Γ |          | X   | X     |         |    |   | Γ.      | 78   |   | X   | Γ  |     | X   | X  | X |          |

| 19   | Γ        |   |     | X   |          |    | X  | X        | 49   | Γ |          | X   | X     |         |    |   | X       | 79   |   | X   | Γ  |     | X   | X  | X | X        |

| 20   | <u> </u> |   |     | I   |          | X  |    | <b>—</b> | 50   | Γ |          | X   | X     |         |    | X |         | 80   | Γ | X   |    | X   |     |    |   |          |

| 21   | Γ        |   |     | X   |          | X  | Γ_ | X        | 51   | Г |          | X   | X     |         |    | I | X       | 81   |   | X   |    | X   |     |    |   | X        |

| 22   |          |   |     | I   | <u> </u> | X  | X  | -        | 52   | T |          | X   | X     |         | X  |   |         | 82   | Π | X   | Γ  | X   |     |    | X |          |

| 23   | 1        |   |     | X   |          | X  |    | X        | 53   | Г |          | X   | X     |         | X  |   | X       | 83   |   | X   |    | X   |     |    | I | X        |

| 24   | Γ        |   |     | X   | X        |    |    |          | 54   |   |          | X   | X     |         | X  | X |         | 84   |   | X   | Γ  | X   |     | X  |   |          |

| 25   | 1        |   |     | X   | X        |    | 1  | X        | 55   | Γ |          | X   | X     |         | X  | X | X       | 85   |   | X   |    | X   |     | X  |   | X        |

| 26   |          |   |     | X   | X        |    | X  |          | 56   | Г |          | X   | X     | X       |    |   |         | 86   | Γ | I   |    | X   |     | X  | X | <u> </u> |

| 27   | 1        |   |     |     | X        | 1  |    | x        | 57   | 1 |          | X   | X     | X       |    |   | X       | 87   | Γ | X   | Γ  | X   |     | X  |   | X        |

| 28   | Γ        |   |     | X   | X        | X  | 1  |          | 58   | Γ |          | X   | X     | X       |    | X |         | 88   | Γ | X   |    | X   | X   |    |   |          |

| 29   | <u> </u> |   |     | X   | X        | X  |    | X        | 59   | I |          | X   | X     | X       |    | X | X       | 89   | Γ | X   |    | X   | X   |    |   | X        |

| 30   | 1        | Π |     | X   | X        | X  | X  | [        | 60   |   |          | X   | I     | X       | X  |   |         | 90   | Γ | X   | Γ. | X   | X   |    | X |          |

I = Switch in the ON position

#### **Communication Port Configuration DIP Switches**

The top group of eight DIP switches on the right side of the DCU determines the set-up parameters for the communication port (refer to Figure 2.2 for location of the switches). The settings for the communication set-up parameters are shown in Table 2.1. To execute the Loop Back Test, the ON/OFF-LINE SWITCH must be in the OFF-LINE mode. Switches 7 and 8 are not used.

| Table 2.1 COMMUNICATIONS PORT CONFIGURATIO | ON DIP-SWITCH SETTINGS |

|--------------------------------------------|------------------------|

|--------------------------------------------|------------------------|

| DATA RATE SELECTION (BPS) *300 1200 9600 19.2 k                                                                                       | DIP-SWITCH NUMBER<br>1 2<br>OFF OFF<br>ON OFF<br>OFF ON<br>ON ON |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| PARITY SELECTION<br>Parity ENABLED (Odd parity<br>generated and checked).<br>*Parity DISABLED (No parity<br>is generated or checked). | DIP-SWITCH NUMBER<br>3<br>ON<br>OFF                              |

| LOOP-BACK TEST<br>(Special Connector Required)<br>Enabled<br>*Disabled                                                                | DIP-SWITCH NUMBER<br>4<br>O N<br>OFF                             |

| TURN-AROUND DELAY<br>* 0 ms delay<br>10 ms delay                                                                                      | DIP-SWITCH NUMBER<br>5<br>OFF<br>ON                              |

| POWER-UP MODE**<br>Program/Stop Mode<br>*Run Mode                                                                                     | DIP-SWITCH NUMBER<br>6<br>ON<br>OFF                              |

\*Factory set defaullt position.

\*\*See sect ion, Power Cycle Conditions Affecting System Operation.

#### EXTERNAL POWER SUPPLY CONNECTOR

The external power supply connector (see Figure 2.2) allows the DCU to receive its operating power (5V dc at 0.5A) from an external power supply. A three conductor cable is provided with the DCU for external power supply connection. Its color code is as follows:

White: +5 V dc (+/-5%) at 0.5 amps Black: Logic ground of power supply Green: Power system ground

#### POWER SUPPLY SELECT SWITCH

There is a power supply select switch on the back of the module to select internal (CPU) or external power for the DCU. An adjacent label indicates correct switch orientation for each selection.

#### USING THE OCU WITH CPU RACK POWER

It is recommended that a Series One high-capacity power supply, IC610CHS110A, 114A, 120A, or 124A be used when installing a DCU in a system. If a high-capacity power supply is not used, then the DCU should be powered by an external +5V dc power supply. If a standard (low capacity) Series One power supply is used with the DCU, inconsistent CPU or communications operation will result.

#### NOTE

Even if a high-capacity power supply is being used in the CPU rack, inconsistent CPU or communications operation may be observed depending on the number and unit load of I/O modules installed in the rack. Refer to Tables 2.2 and 2.3 for units of load supplied by the different racks and used by I/O modules and other system devices

Table 2.2 SERIES ONE UNITS\* Of LOAD (SUPPLIED)

| CATALOG NUMBER | DESCRIPTION           | POW   | ER SUPPLIED | IN UNITS OF | F LOAD    |

|----------------|-----------------------|-------|-------------|-------------|-----------|

|                |                       | +5 v  | +9 v        | +24 v       | +24 V EXT |

| IC6lOCHSl00A   | 5-slot std cap        | 40    | 80          | 20          | -         |

| IC610CHSll0A   | 5-slot hi cap         | 140   | 80          | 40**        | 10        |

| IC6l0CHS114A   | 5-slot hi cap 24 V de | c 140 | 80          | 40          |           |

| IC610CHS120A   | l0-slot hi cap        | 140   | 160         | 40**        | 10        |

| IC610CHS124A   | 10-slot hi cap 24 V d | c 140 | 160         | 40          |           |

| IC610CHS130A   | l0-slot hi cap        | 140   | 170         | 50**        | 10        |

| IC610CHS134A   | 10-slot hi cap 24 V d | c 140 | 170         | 50          |           |

\* 1 unit = 10 mA

\*\* If an external sensor is connected to the 24 V + and - terminals on the power supply, the current used by the sensor (up to a maximum of 100 mA), should be deducted from the available listed units of load.

| ATALOG NUMBER | DESCRIPTION<br>(CIRCUITS)                                                                      |       | USED IN UNITS<br>+9 V |           |

|---------------|------------------------------------------------------------------------------------------------|-------|-----------------------|-----------|

|               | (01100110)                                                                                     |       |                       | · _ · _ · |

| C610CPU101C   | CPU                                                                                            | 25    | -                     | -         |

| C610CPU105A   | CPU                                                                                            | 25    | -                     | -         |

| C610PRG100B   | Programmer                                                                                     | 6     | 5                     | -         |

| C610PRG105A   | Programmer                                                                                     | 6     | 5                     | -         |

| C610MDL101A   | Inp 24 V dc sink (8)                                                                           | -     | 1                     | 10        |

| C610MDL102A   | Inp 24 V dc src (16)                                                                           | -     | 2                     | 19        |

| C610MDL103A   | I/O 24 V dc (4/4)                                                                              | -     | 2                     | 7         |

| C610MDL104A   | I/O 24 V dc (4/4)<br>I/Relay Out 24 V dc (4/4)                                                 | -     | 20                    | 6         |

| C610MDL105A   | Inumpwheel Interi (4x10)                                                                       | -     | 1                     | 10        |

| C610MDL106A   | Inp 24 V dc sink w LEDs (1                                                                     | l6) — | 3                     | 24        |

| C610MDL107A   | Inp 24 V dc sink load (16)                                                                     | ) –   | 3                     | 23        |

| C610MDL110A   | HI Speed Counter LLI                                                                           | -     | /                     | -         |

| C610MDL111A   | Inp 24 V ac/dc (8)                                                                             | -     | 1                     | -         |

| C610MDL112A   | Inp 24 V ac/dc (8)<br>Inp 24 V ac/dc souce (16)                                                | -     |                       |           |

| C610MDL115A   | I/O Fast Response $(4/2)$                                                                      | _     | 8                     | 6         |

| C610MDL124A   | I/O Simulator (8)<br>Inp 115 V ac (8)<br>Inp 115 V ac isolated (4)                             | _     | 1                     | 11        |

| C610MDL125A   | Inp 115 V ac (8)                                                                               | -     | 1                     | -         |

| C610MDL126A   | Inp 115 V ac isolated (4)<br>Inp 230 V ac (8)<br>Out 24 V dc sink (8)<br>Out 24 V dc sink (16) | -     | 1                     | -         |

| C610MDL127A   | Inp 230 V ac (8)                                                                               | _     | 1                     | -         |

| C610MDL151A   | Out 24 V dc sink (8)                                                                           | -     | 2                     | 3         |

| C610MDL152A   | Out 24 V dc sink (16)                                                                          | _     | 5                     | 4         |

| C610MDL153A   | Out 24 V dc sink $(4)$                                                                         | _     | 1                     | 1         |

| C610MDL154A   | Out 24 V dc sink/src (4)                                                                       | -     | 1                     | 10        |

| C610MDL155A   | Out 24 V dc src $(8)$                                                                          | _     | 3                     | _         |

| C610MDL156A   | Out 24 V dc sink w LEDs (1                                                                     | L6) – | 4                     | 10        |

| C610MDL157A   | Out 24 V dc sink w LEDs (1                                                                     |       | 4                     | 10        |

| C610MDL158A   | Out 24 V dc src w LEDs (1                                                                      |       | 20                    | _         |

| C610MDL175A   | Out 115/230 V ac (8)                                                                           | -     | 16                    | _         |

| C610MDL176A   | Out 115/230 V ac isol (4)                                                                      | -     | 8                     | _         |

| C610MDL180A   | Out Relay (8)                                                                                  | _     | 34                    | -         |

| C610MDL182A   | Out Relay (16)                                                                                 | -     | 48                    | -         |

| C610CCM100A   | Data Comms Unit                                                                                | 30    | _                     | _         |

| C610CCM105A   | Data Comms Unit                                                                                | 30    | -                     | -         |

| C610CCM110A   | I/O Link Local Module                                                                          | 60    | _                     |           |

| C610CCM111A   | -                                                                                              |       | _                     | -         |

| C610PER151A   |                                                                                                | 26    | _                     | _         |

|               | Low Cost PROM Writer                                                                           | 80    |                       |           |

Table 2.3 SERIES ONE UNITS\* OF LOAD (USED)

\*1 unit = 10 mA. Calculations are based on the worst case--all inputs and outputs on.

•

ane.

-

#### INSTALLING THE DCU

To install the DCU:

- 1. Set the internal/external power switch to the desired position.

- 2. Position the CPU (unit) ID and port configuration DIP switches to the desired position (see Figure 2.3 and Table 2.1).

- 3. With the Series One, Series One Junior, or Series One Plus CPU power off, connect the DCU to the CPU and the programmer to the DCU (if desired) as shown in Figure 2.4.

If, before powering up, the ON-LINE/OFF-LINE switch is placed in the ON-LINE position, after power up the PWR, RUN, and DIAG indicators should light in that order. For more information on power-up conditions affecting the CPU and communications status see Table 2.4.

#### NOTE

The Series One CPU version must be Revision B or later.

#### Figure 2.4 CONNECTING THE PROGRAMMER, DCU, AND CPU

т

#### POWER CYCLE CONDITIONS AFFECTING SYSTEM OPERATION

When power is cycled, the resulting CPU and communications status depends upon the position of the DCU ON-LINE/OFF-LINE switch and power-up mode switch, whether the programmer is attached or detached, the programmer mode switch position, and the condition of the CPU battery. See Table 2.4.

| DCU      | ļ            | PROGF                 | AMMER                           | RESULTING CPU AND COMMUNICATIONS<br>STATUS ON POWER CYCLE                                                                                                                                                                                                                      |

|----------|--------------|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ,        |              | ATTACHED/<br>DETACHED | MODE KEY-<br>SWITCH<br>POSITION |                                                                                                                                                                                                                                                                                |

| On-Line  | Off(Run)     | Attached              | Run                             | CPU in Run mode with communica-<br>tions active.                                                                                                                                                                                                                               |

| On-Line  | On (Prog)    | Attached              | Run                             | CPU in Program mode with<br>communications active only for<br>the following serial requests:<br>Read or command Run/Program and<br>Read Diagnostic Status Words.<br>The DCU will return in the status<br>code a hexadecimal 10 to indicate<br>that a power cycle has occurred. |

| Off-Line | On or<br>Off | Not<br>Attached       |                                 | CPU is in the same mode in which<br>it powered down, communication is<br>inactive since the unit is off<br>line. (Communications will be<br>active on off line to on line<br>transition).*                                                                                     |

| Off-Line | On or<br>Off | Attached              |                                 | CPU is in whatever mode the key-<br>switch is set for with communica-<br>tions not active.                                                                                                                                                                                     |

## Table 2.4 POWER CYCLE CONDITIONS AFFECTING SYSTEM OPERATION (The user program is assumed to be in CMOS RAM).

\* For Series One CPUs versions A or B, the resulting communications status is the same, but the resulting CPU status is that the CPU is in Program mode with the communications inactive.

## NOTE

The following statuses result  $\underline{only}$  when there is a low battery condition in the CPU.

Table 2.4 POWER CYCLE CONDITIONS AFFECTING SYSTEM OPERATION (continued)

|            | POWER UP<br>MODE DIP<br>SWITCH 6 | PROGRA<br>ATTACHED/<br>DETACHED | AMMER<br>MODE KEY-<br>SWITCH<br>POSITION | RESULTING CPU AND COMMUNICATIONS<br>STATUS ON POWER CYCLE                                                                                                                                                                          |

|------------|----------------------------------|---------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off Line O | on or Off                        | Not<br>Attached                 |                                          | CPU in Program mode with communi-<br>cations inactive since unit is off<br>line.                                                                                                                                                   |

| On Line C  | On(Prog)                         | Not<br>Attached                 |                                          | CPU in Program mode with communi-<br>cations active. DIAG LED will be<br>ON and and RUN LED will be OFF.                                                                                                                           |

| -          | Off<br>(Run)                     | Not<br>Attached                 |                                          | CPU in Program mode with communi-<br>cations inactive. DIAG and RUN<br>will be OFF. Unit must be<br>manually set to Program/Stop mode<br>and the E-21 error cleared (if it<br>has occurred) before communica-<br>tions can resume. |

#### CHAPTER 3 INSTALLATION AND OPERATION OF THE DATA COMMUNICATIONS MODULE FOR THE SERIES THREE PC

This chapter describes the operation of the DCM's user interfaces (LEDs, switches, and ports) and the installation of the Data Communications Module (DCM) (IC630CCM300).

## DESCRIPTION AND OPERATION OF THE DCM'S USER INTERFACES

The various indicator lights, connectors, and configuration DIP switches for the DCM are shown in Figure 3.1.

**TPK. A. 40007**

Figure 3.1 FRONT AND REAR VIEW OF THE DCM

### LED INDICATORS

.

The three status LED's on the front of the DCM convey the following information

| Status LED | State | Description                                                                                                                                                  |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA       | On    | Data being transferred to/from the communication port.                                                                                                       |

|            | Off   | Data not being transferred to/from the communication port or data incorrect due to:                                                                          |

|            |       | <ol> <li>Parity overrun or framing errors;</li> <li>Invalid header, data block, control character, or checksum;</li> <li>Time out on serial sink.</li> </ol> |

| DIAG       | 0 n   | Power-up hardware diagnostics have passed.                                                                                                                   |

|            | Off   | Power-up hardware diagnostics have failed.                                                                                                                   |

| PWR        | On    | 5 V dc power to DCM is connected.                                                                                                                            |

|            | Off   | 5 V dc power to DCM is not connected.                                                                                                                        |

#### NOTE

Power to the DCM can come from the Series Three CPU or external supply depending on position of power select switch. When the power supply select switch is in the EXT position, power must be supplied through the external power supply connector on the front of the DCM. See Figure 3.1.

#### FRONT PANEL CONNECTORS

Three connectors on the front of the DCM provide an interface to:

- 1. Series Three CPU (CPU Connector);

- 2. External serial device (Communications Connector); and

- 3. External power supply.

Each of these interfaces are described below.

#### Series Three CPU Connector

The CPU connector (25-pin male, D-type) ties the DCM to the Series Three CPU. All communication with the Series Three, as well as operating power (if the power supply select switch is set to internal) is transmitted through this interface. The cable (IC630CBL395A) is provided with each DCM for the link.

#### Communications Connector

The communications connector (25-pin female, D-type) connects the DCM to external devices. A detailed description (pin by pin) of this connector is shown in Chapter 4.

#### External Power Supply Connector

The external power supply connector allows the DCM to receive its operating power (5 V dc at 0.5 A) from an external supply. Users with Series Three power supply IC630PWR300A require an external power supply to operate a DCM. Other Series Three power supplies may or may not necessitate the use of an external power supply for proper operation of the DCM. This is dependent on the number and type of I/O modules in the CPU rack. Refer to Tables 3.2 and 3.3. A three conductor cable is provided with the DCM for external power supply connection. Its color code is as follows:

| WHITE: | +5V DC ( <del>+/</del> 5%) at 0.5 amps |

|--------|----------------------------------------|

| BLACK: | Logic ground of power supply           |

| GREEN: | Power system ground.                   |

#### DCM CONFIGURATION SWITCHES

The ON/OFF line switch is located on the front of the DCM. The other configuration switches are located on the back of the DCM as shown below.

Figure 3.2 LOCATION OF THE DCM CONFIGURATION SWITCHES

#### **ON/OFF-LINE** Switch

The ON/OFF-line switch which is recessed on the front panel of the DCM enables or disables the serial communications with the Series Three CPU.

- OFF LINE: Serial communication between the DCM and CPU is disabled, and the CPU is under control of the programmer.

- ON LINE: Serial communication between the DCM and CPU is enabled, and the programmer is not functional.

#### NOTE

The terminal LED indicator on the face of the Series Three identifies **the** status of the serial link between the DCM and CPU.

Terminal LED ON:DCM/CPU interface enabled.Terminal LED OFF:DCM/CPU interface disabled.

#### Interaction between the DCM ON/OFF-LINE switch and the CPU Keyswitch

In order to establish or maintain the serial link between the DCM and the Series Three CPU, the CPU keyswitch must be in the Run 1 or Run position, and the DCM ON/OFF-LINE switch in the ON-LINE position. If the CPU keyswitch is ever taken out of the Run position when the serial link is enabled, the link will become disabled and the TERMINAL LED will turn off.

To re-enable communications:

- 1. Put the CPU keyswitch back in Run 1 or Run position.

- 2. Cycle the ON/OFF-LINE switch on the DCM with the final position being ON LINE.

#### NOTE

Once the link is established and the TERMINAL LED is on, the Series Three CPU can be put in either Stop/Program or Run mode by a serial request from the master device on the link. See the application examples in Chapter 5.

#### CPU (Unit) ID DIP Switches

The top group of eight DIP switches located on the back of the DCM (see Figure 3.2), determine the CPU ID of 1-90. The switch configuration associated with each ID is shown in Figure 3.3.

| UNIT |    |   |   | SW. |   |    |   |   | UNIT | 1   | DII |           |     |     |   |   |   | UNIT | I |   |   | SW) |   |   |   |   |

|------|----|---|---|-----|---|----|---|---|------|-----|-----|-----------|-----|-----|---|---|---|------|---|---|---|-----|---|---|---|---|

| ID   |    | P |   | IT: |   |    |   | _ | ID   |     | P   | <u>25</u> | LT] | [0] | 1 |   | _ | ID   |   |   |   | IT  |   |   |   |   |

|      | 8  | 1 | 6 | 5   | 4 | 3  | 2 | 1 | l    | 8   | 1   | 6         | 5   | 4   | 3 | 2 | 1 |      | 8 | 1 | 6 | 5   | 4 | 3 | 2 | 1 |

| 1    | Γ. |   |   |     | L |    |   | X | 31   |     |     |           | X   | X   | X | X | X | 61   |   |   | X | X   | X | X |   | X |

| 2    | Γ. |   |   |     |   |    | X |   | 32   |     |     | X         |     |     |   |   |   | 62   |   |   |   | X   |   |   |   |   |

| 3    |    |   |   |     |   |    | X | X | 33   |     |     | X         |     |     |   | L | X | 63   |   |   | X | X   | X | X | X | X |

| 4    |    |   |   |     |   | X  |   |   | 34   | i . | Ĺ   | X         |     |     |   | X |   | 64   |   | X |   |     |   |   |   |   |

| 5    | Γ. |   |   |     | L | X  | L | X | 35   | L   |     | X         |     |     |   | X | X | 65   |   | X |   |     |   |   |   | X |

| 6    |    |   |   |     |   | X  | X |   | 36   |     | -   | X         |     |     | I |   |   | 66   |   | X |   |     |   |   | I | [ |

| 1    | I. |   | Ι |     |   | X  | X | X | 37   |     |     | I         |     |     | X |   | X | 67   |   | X |   |     |   |   | X | X |

| 8    |    |   | Γ |     | X | Γ  | Ι |   | 38   | Γ   |     | X         |     |     | X | X | 1 | 68   |   | X |   |     |   | X |   |   |

| 9    | T  |   | Γ |     | X |    |   | X | 39   | I   | Γ   | X         |     |     | X | X | X | 69   |   | X |   |     |   | I |   | X |

| 10   | Γ. |   | Ι | I   | X | Ι. | X |   | 40   |     |     | X         | I   | I   |   |   |   | 70   |   | X | L |     |   | X | X |   |

| 11   | Γ  |   |   |     | X |    | X | X | 41   | I   |     | X         |     | X   |   |   | I | 71   |   | X |   |     |   | X | X | X |

| 12   |    |   |   |     | X | X  |   |   | 42   | ]   |     | I         |     | I   |   | X |   | 72   |   | I |   |     | X |   |   |   |

| 13   | Γ  |   |   |     | X | X  |   | X | 43   |     |     | X         |     | X   |   | X | I | 73   |   | X |   |     | X |   |   | X |

| 14   |    |   |   |     | X | X  | X |   | 44   |     |     | X         |     | X   | X |   |   | 74   |   | X |   |     | X |   | X |   |

| 15   |    |   |   |     | X | X  | X | X | 45   |     |     | X         |     | X   | X |   | X | 75   |   | X |   |     | X |   | X | X |

| 16   |    |   |   | X   | E |    |   |   | 46   |     |     | X         |     | X   | X | X |   | 76   |   | X |   |     | X | I |   |   |

| 17   | Γ  |   |   | X   | Γ |    | Γ | X | 47   | I   |     | X         |     | X   | X | X | X | 77   |   | X |   |     | X | X |   | X |

| 18   |    |   |   | X   |   |    | X |   | 48   |     |     | X         | X   |     |   |   |   | 78   |   | X |   |     | X | X | X |   |

| 19   |    |   |   | X   |   |    | X | X | 49   |     |     | X         | X   |     |   |   | X | 79   |   | X |   |     | X | X | X | X |

| 20   |    |   |   | X   |   | X  |   |   | 50   | Γ   |     | X         | X   |     |   | X |   | 80   |   | X |   | X   |   |   |   |   |

| 21   |    |   |   | X   |   | X  |   | I | 51   | Γ   |     | X         | X   |     |   | I | X | 81   |   | X |   | X   |   |   |   | X |

| 22   |    |   |   | X   |   | X  | X |   | 52   |     |     | I         | X   |     | I |   |   | 82   |   | X |   | X   |   |   | X |   |

| 23   | Γ  |   |   | X   |   | X  | X | X | 53   | Γ   |     | X         | X   |     | X |   | X | 83   |   | I |   | X   |   |   | X | X |

| 24   | T  |   |   | X   | I | Γ  |   |   | 54   | Γ   |     | X         | X   |     | X | X |   | 84   |   | X |   | X   |   | X |   |   |

| 25   |    |   |   | X   | X |    |   | X | 55   | 1   |     | X         | X   |     | I | X | X | 85   |   | I |   | X   |   | X |   | X |

| 26   | 1  |   |   | I   | - |    | X |   | 56   |     |     | X         | X   | X   |   | Γ |   | 86   |   | X |   | X   |   | X | X |   |

| 27   | 1  | - | Γ | X   |   | T  |   | X | 57   | 1   |     | X         | X   | • • |   |   | I | 87   |   | X | Π | X   |   | X | X | X |

| 28   | Γ  |   |   | X   | X | X  |   | Ľ | 58   | Ι   | Γ   | X         | X   | X   |   | X |   | 88   |   | X |   | X   | X |   |   |   |

| 29   |    |   |   | I   | X | X  |   | X | 59   | Γ   |     | X         | X   | X   |   | I | X | 89   |   | X |   | X   | X |   |   | X |

| 30   |    |   |   | X   | X | X  | X |   | 60   | Γ   |     | I         | X   | I   | X |   |   | 90   |   | X |   | X   | X |   | X |   |

$\mathbf{X}$  = Switch in the ON position

•

Figure 3.3 DIP-SWITCH SETTINGS FOR CPU ID SELECTION

TPK.A.40223

#### **Communication Port Configuration DIP Switches**

The bottom group of eight DIP switches on the back of the DCM selects the mode of operation for the communication port (refer **to** Figure 3.2 for location of switches). The various settings for the communication set up parameters are shown in Table 3.1. To execute the loop-back test the ON/OFF-LINE switch must in the Off-Line mode.

| DATA RATE SELECTION (BPS) *300 1200 9600 19.2 k                                                                                       | DIP-SWITCH NUMBER<br>1 2<br>OFF OFF<br>ON OFF<br>OFF ON<br>ON ON |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| PARITY SELECTION<br>Parity ENABLED (Odd parity<br>generated and checked).<br>*Parity DISABLED (No parity<br>is generated or checked). | DIP-SWITCH NUMBER<br>3<br>ON<br>OFF                              |

| LOOP-BACK TEST<br>(Special Connector Required)<br>Enabled<br>*Disabled                                                                | DIP-SWITCH NUMBER<br>4<br>O N<br>OFF                             |

| TURN-AROUND DELAY<br>* 0 ms delay<br>10 ms delay                                                                                      | DIP-SWITCH N-UMBER<br>5<br>OFF<br>ON                             |

| KEYING SIGNAL<br>Enabled<br>*Disabled                                                                                                 | DIP-SWITCH NUMBER<br>6<br>ON<br>OFF                              |

Table 3.1 COMMUNICATIONS PORT CONFIGURATION DIP-SWITCH SETTINGS

\*Factory set default position.

#### POWER SUPPLY SELECT SWITCH

There is a power supply select switch on the back of the module for the selection of internal (CPU) or external power for the DCM. An adjacent label indicates correct switch orientation for each selection. See the section, External Power Supply Connector, in this chapter for information on the installation of an external power supply.

#### USING THE DCM WITH CPU RACK POWER

Users with Series Three power supply IC630PWR300A require an external 5 V dc power supply to operate the DCM. If power supply IC630PWR300A is used with the DCM, inconsistent CPU or communications operation will result.

#### NOTE

Even if a high-capacity power supply is being used in the CPU rack, inconsistent CPU or communications operation may be observed depending on the number and unit load of I/O modules installed in the rack. Refer to Tables 3.2 and 3.3 for units of load supplied by the different racks and used by I/O modules and other system devices.

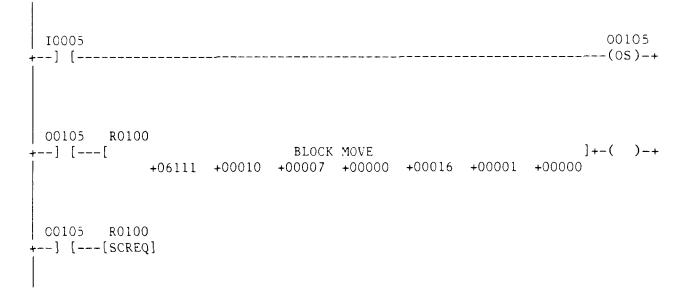

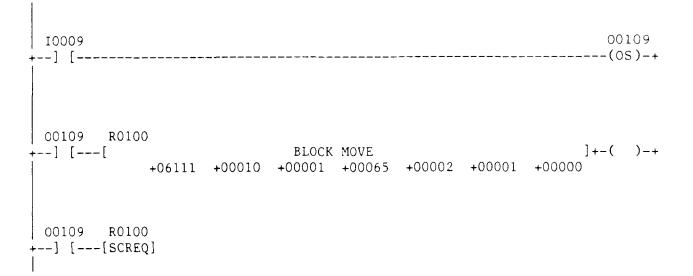

| CATALOG NUMBER                                                               | DESCRIPTION                                                                                                                               | POWER | SUPPLIED<br>+5v                        | IN UNITS OF LOAD<br>+12v               |