# **GE Fanuc Automation**

Programmable Control Products

Series 90<sup>™</sup>-30/20/Micro PLC CPU Instruction Set

**Reference Manual**

GFK-0467L

June 1999

# Warnings, Cautions, and Notes as Used in this Publication

# Warning

Warning notices are used in this publication to emphasize that hazardous voltages, currents, temperatures, or other conditions that could cause personal injury exist in this equipment or may be associated with its use.

In situations where inattention could cause either personal injury or damage to equipment, a Warning notice is used.

Caution

Caution notices are used where equipment might be damaged if care is not taken.

#### Note

Notes merely call attention to information that is especially significant to understanding and operating the equipment.

This document is based on information available at the time of its publication. While efforts have been made to be accurate, the information contained herein does not purport to cover all details or variations in hardware or software, nor to provide for every possible contingency in connection with installation, operation, or maintenance. Features may be described herein which are not present in all hardware and software systems. GE Fanuc Automation assumes no obligation of notice to holders of this document with respect to changes subsequently made.

GE Fanuc Automation makes no representation or warranty, expressed, implied, or statutory with respect to, and assumes no responsibility for the accuracy, completeness, sufficiency, or usefulness of the information contained herein. No warranties of merchantability or fitness for purpose shall apply.

The following are trademarks of GE Fanuc Automation North America, Inc.

Alarm Master CIMPLICITY CIMPLICITY 90–ADS CIMSTAR Field Control GEnet Genius Helpmate Logicmaster Modelmaster Motion Mate ProLoop PROMACRO PowerMotion PowerTRAC Series 90 Series Five Series One Series Six Series Three VersaMax VersaPro VuMaster Workmaster

©Copyright 1989–1999 GE Fanuc Automation North America, Inc. All Rights Reserved. This manual describes the system operation, fault handling, and Logicmaster 90<sup>TM</sup> programming instructions for the Series 90<sup>TM</sup>-30, Series 90-20 and Series 90 Micro programmable logic controllers. Series 90-30 PLCs, Series 90-20 PLCs, and Series 90 Micro PLCs are members of the Series 90 family of programmable logic controllers from GE Fanuc Automation.

## **Revisions to This Manual**

- The Model 364 CPU (release 9.0 and later) supports connection to an Ethernet network through either of two built-in Ethernet ports. AAUI and 10BaseT ports are provided. The Model 364 is the only Series 90-30 CPU that supports Ethernet Global Data (p. 2-39).

- The Hand Held Programmer does not allow you to change the Time of Day clock while key switch protection is active (p. 2-14).

- Sweep impact figures for DSM configuration have been added to Chapter 2.

- Differences in operation for Logarithmic/Exponential (p. 6-12) and Truncate (p. 11-11) functions have been identified for the CPU352.

- The Sequential Event Recorder (SER) discussion has been revised to clarify the capabilities of this function. Detailed timing information for this function is provided in Appendix A. This function is available on release 9.0 and later of the 35x and 36x series CPUs (p. 12-8).

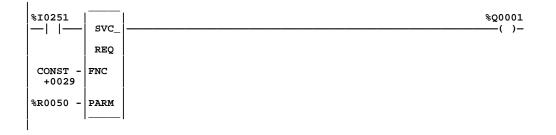

- A new service request, Skip Next Output and Input Scan (SVCREQ #45) is available for release 9.0 and later of the 35x and 36x series CPUs (p. 12-63).

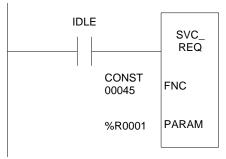

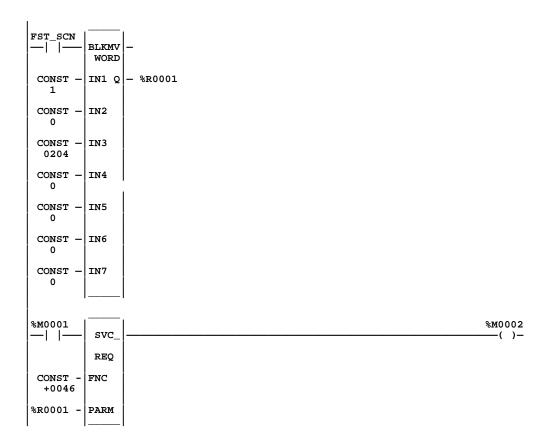

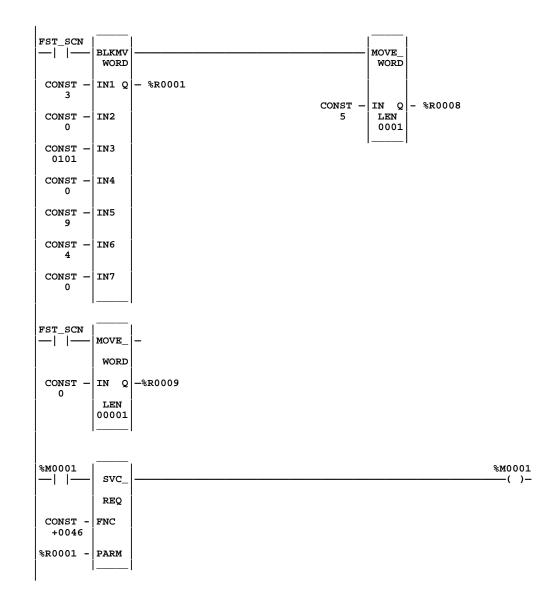

- The parameter block listings for read and write functions of the Fast Backplane Status Access service request (SVCREQ #46) have been corrected (p. 12-64).

- Other corrections and clarifications as necessary.

# **Content of This Manual**

**Chapter 1. Introduction:** provides an overview of the Series 90-30 PLC, the Series 90-20 PLC, and the Series 90 Micro PLC systems and the Series 90-30/20/Micro instruction set.

**Chapter 2. System Operation:** describes certain system operations of the Series 90-30 PLC, Series 90-20 PLC, or Series 90 Micro systems. This includes a discussion of the PLC system sweep sequences, the system power-up and power-down sequences, clocks and timers, security, I/O, and fault handling. It also includes general information for a basic understanding of programming ladder logic.

**Chapter 3. Fault Explanations and Correction:** provides troubleshooting information for a Series 90-30, 90-20, or Micro PLC system. It explains fault descriptions in the PLC fault table and fault categories in the I/O fault table.

**Chapters 4-12. Series 90-30/20/Micro Instruction Set:** describe programming instructions available for Series 90-30 PLCs, Series 90-20 PLCs, and Series 90 Micro PLCs. These chapters correspond to the main program function groups.

**Appendix A. Instruction Timing:** lists the memory size in bytes and execution time in microseconds for each programming instruction. Memory size is the number of bytes required by the function in a ladder diagram application program.

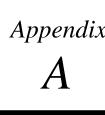

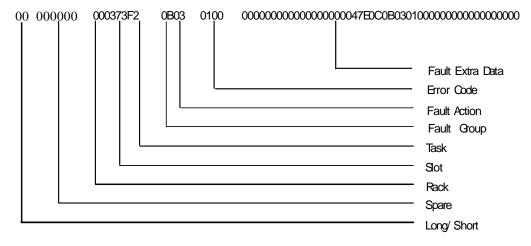

**Appendix B. Interpreting Fault Tables:** describes how to interpret the message structure format when reading the fault tables using Logicmaster 90-30/20/Micro software.

**Appendix C. Instruction Mnemonics:** lists mnemonics that can be typed to display programming instructions while searching through or editing a program.

**Appendix D. Key Functions:** lists the special keyboard assignments used for the Logicmaster 90-30/20/Micro software. A *pull-out quick reference card* that lists key functions and instruction mnemonics follows this appendix.

**Appendix E. Using Floating-Point Numbers:** describes special considerations for using floating-point math operations.

### **Related Publications**

Logicmaster<sup>TM</sup> 90 Series 90<sup>TM</sup>-30/20/Micro Programming Software User's Manual (GFK-0466).

Logicmaster™ 90 Series 90-30 and 90-20 Important Product Information (GFK-0468).

Series 90TM-30 Programmable Controller Installation Manual (GFK-0356).

Series 90<sup>™</sup>-20 Programmable Controller Installation Manual (GFK-0551).

Series 90<sup>TM</sup>-30 I/O Module Specifications Manual (GFK-0898).

*Series* 90<sup>TM</sup> *Programmable Coprocessor Module and Support Software User's Manual* (GFK-0255).

Series 90<sup>™</sup> PCM Development Software (PCOP) User's Manual (GFK-0487). CIMPLICITY<sup>™</sup> 90-ADS Alphanumeric Display System User's Manual (GFK-0499). CIMPLICITY<sup>™</sup> 90-ADS Alphanumeric Display System Reference Manual (GFK-0641). Alphanumeric Display Coprocessor Module Data Sheet (GFK-0521). Series 90<sup>™</sup>-30 and 90-20 PLC Hand-Held Programmer User's Manual (GFK-0402). Power Mate APM for Series 90<sup>™</sup>-30 PLC—Standard Mode User's Manual (GFK-0840). Power Mate APM for Series 90<sup>™</sup>-30 PLC—Follower Mode User's Manual</sup> (GFK-0781). Motion Mate<sup>™</sup> DSM302 for Series 90<sup>™</sup>-30 PLCs User's Manual (GFK-1464) Series 90<sup>™</sup>-30 High Speed Counter User's Manual (GFK-0293).

Series 90<sup>™</sup>-30 Genius Communications Module User's Manual (GFK-0412).

Genius Communications Module Data Sheet (GFK-0272).

Series 90<sup>TM</sup>-30 Genius<sup>TM</sup> Bus Controller User's Manual (GFK-1034).

Series 90<sup>TM</sup>-70 FIP Bus Controller User's Manual (GFK-1038).

Series 90<sup>TM</sup>-30 FIP Remote I/O Scanner User's Manual (GFK-1037).

Field Control<sup>TM</sup> Distributed I/O and Control System Genius<sup>TM</sup> Bus Interface Unit User's Manual (GFK-0825).

Series 90<sup>TM</sup> Micro Programmable Logic Controller User's Manual (GFK-1065).

Series 90<sup>TM</sup> PLC Serial Communications User's Manual (GFK-0582).

# We Welcome Your Comments and Suggestions

At GE Fanuc Automation, we strive to produce quality technical documentation. After you have used this manual, please take a few moments to complete and return the Reader's Comment Card located on the next page.

Libby Allen Sr. Technical Writer

| Chapter 1 | Introduction                                                         | 1-1  |

|-----------|----------------------------------------------------------------------|------|

| Chapter 2 | System Operation                                                     | 2-1  |

|           | Section 1: PLC Sweep Summary                                         | 2-2  |

|           | Standard Program Sweep                                               |      |

|           | Sweep Time Calculation                                               | 2-7  |

|           | Programmer Communications Window                                     |      |

|           | System Communications Window                                         |      |

|           | PCM Communications with the PLC (Models 331 and Higher)              |      |

|           | DSM Communications with the PLC                                      |      |

|           | Standard Program Sweep Variations                                    |      |

|           | Constant Sweep Time Mode                                             |      |

|           | PLC Sweep When in STOP Mode                                          |      |

|           | Communication Window Modes                                           |      |

|           | Key Switch on 35x and 36x Series CPUs: Change Mode and Flash Protect |      |

|           | Using the Release 7 and Later Key Switch                             |      |

|           | Clearing the Fault Table with the Key Switch                         |      |

|           | Enhanced Memory Protect with Release 8 and Later CPUs                | 2-16 |

|           | Section 2: Program Organization and User References/Data             | 2-17 |

|           | Subroutine Blocks                                                    |      |

|           | Examples of Using Subroutine Blocks                                  |      |

|           | How Blocks Are Called                                                |      |

|           | Periodic Subroutines                                                 |      |

|           | User References                                                      |      |

|           | Transitions and Overrides                                            |      |

|           | Retentiveness of Data                                                |      |

|           | Data Types                                                           |      |

|           | System Status References                                             |      |

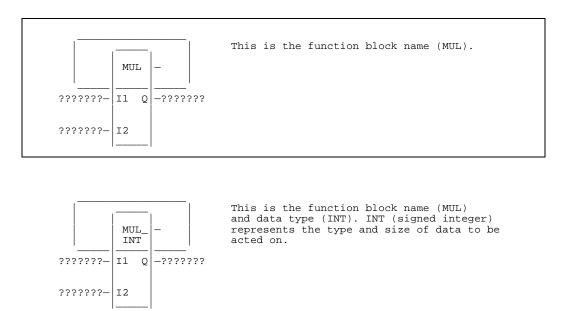

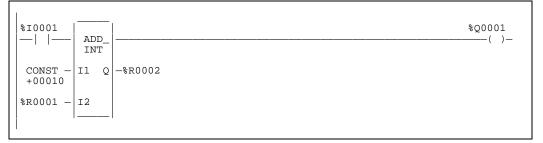

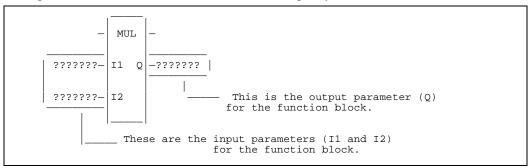

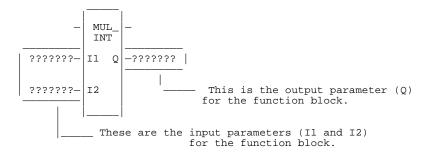

|           | Function Block Structure                                             |      |

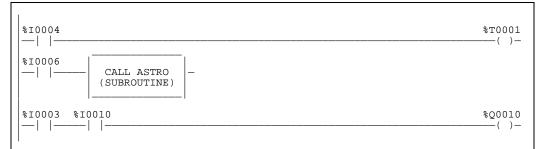

|           | Format of Ladder Logic Relays                                        |      |

|           | Format of Program Function Blocks                                    |      |

|           | Function Block Parameters                                            |      |

|           | Power Flow In and Out of a Function                                  |      |

|           | Section 3: Power-Up and Power-Down Sequences                         | 2-30 |

|           | Power-Up                                                             |      |

|           | Power-Down                                                           |      |

|           | Section 4: Clocks and Timers                                         | 2-34 |

|           | Elapsed Time Clock                                                   |      |

|           | Time-of-Day Clock                                                    |      |

|           | Watchdog Timer                                                       |      |

|           | Elapsed Power Down Timer                                             |      |

|           | Constant Sweep Timer                                 |      |

|-----------|------------------------------------------------------|------|

|           | Time-Tick Contacts                                   | 2-36 |

|           | Section 5: System Security                           | 2-37 |

|           | Passwords                                            | 2-37 |

|           | Privilege Level Change Requests                      | 2-38 |

|           | Locking/Unlocking Subroutines                        | 2-38 |

|           | Permanently Locking a Subroutine                     | 2-38 |

|           | Section 6: Series 90-30, 90-20, and Micro I/O System | 2-39 |

|           | Series 90-30 I/O Modules                             |      |

|           | I/O Data Formats                                     | 2-42 |

|           | Default Conditions for Series 90-30 Output Modules   | 2-42 |

|           | Diagnostic Data                                      | 2-42 |

|           | Global Data                                          | 2-43 |

|           | Genius Global Data                                   |      |

|           | Ethernet Communications                              |      |

|           | Model 20 I/O Modules                                 |      |

|           | Configuration and Programming                        | 2-44 |

| Chapter 3 | Fault Explanation and Correction                     |      |

|           | Section 1: Fault Handling                            |      |

|           | Alarm Processor                                      |      |

|           | Classes of Faults                                    |      |

|           | System Reaction to Faults                            |      |

|           | Fault Tables                                         |      |

|           | Fault Action                                         |      |

|           | Fault References                                     |      |

|           | Fault Reference Definitions                          |      |

|           | Additional Fault Effects                             |      |

|           | PLC Fault Table Display                              |      |

|           | I/O Fault Table Display                              |      |

|           | Accessing Additional Fault Information               |      |

|           | Section 2: PLC Fault Table Explanations              |      |

|           | Fault Actions                                        |      |

|           | Loss of, or Missing, Option Module                   |      |

|           | Reset of, Addition of, or Extra, Option Module       |      |

|           | System Configuration Mismatch                        |      |

|           | Option Module Software Failure                       |      |

|           | Program Block Checksum Failure                       |      |

|           | Low Battery Signal                                   |      |

|           | Constant Sweep Time Exceeded                         |      |

|           | Application Fault                                    |      |

|           | No User Program Present                                  |     |

|-----------|----------------------------------------------------------|-----|

|           | Corrupted User Program on Power-Up                       |     |

|           | Password Access Failure                                  |     |

|           | PLC CPU System Software Failure                          |     |

|           | Communications Failure During Store                      |     |

|           | Section 3: I/O Fault Table Explanations                  |     |

|           | Loss of I/O Module                                       |     |

|           | Addition of I/O Module                                   |     |

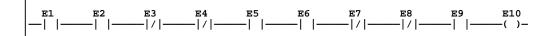

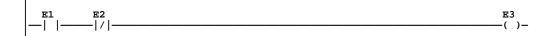

| Chapter 4 | Relay Functions                                          | 4-1 |

|           | Using Contacts                                           | 4-1 |

|           | Using Coils                                              |     |

|           | Normally Open Contact —                                  |     |

|           | Normally Closed Contact —  / —                           |     |

|           | Coil —()—                                                |     |

|           | Example                                                  |     |

|           | Negated Coil —(/)—                                       | 4-4 |

|           | Example                                                  | 4-4 |

|           | Retentive Coil —(M)—                                     | 4-4 |

|           | Negated Retentive Coil —(/M)—                            | 4-4 |

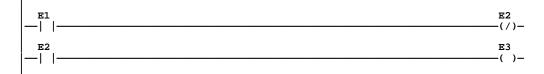

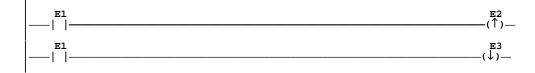

|           | Positive Transition Coil $-(\uparrow)$                   | 4-4 |

|           | Negative Transition Coil $-(\downarrow)$                 | 4-5 |

|           | Example                                                  |     |

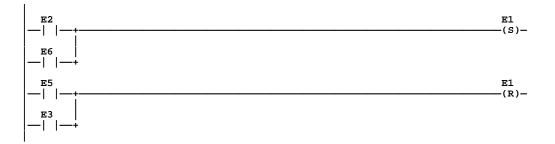

|           | SET Coil —(S) —                                          | 4-5 |

|           | RESET Coil —(R)—                                         |     |

|           | Example                                                  |     |

|           | Retentive SET Coil —(SM)—                                |     |

|           | Retentive RESET Coil —(RM)—                              |     |

|           | Links                                                    | 4-7 |

|           | Example                                                  | 4-7 |

|           | Continuation Coils (———————————————————————————————————— |     |

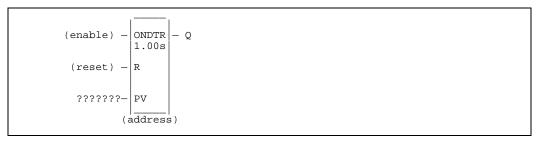

| Chapter 5 | Timers and Counters                                      | 5-1 |

|           | Function Block Data Required for Timers and Counters     | 5-1 |

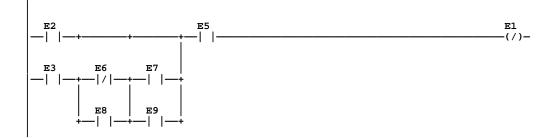

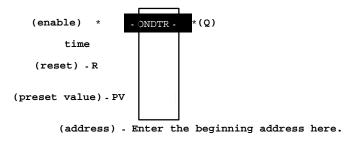

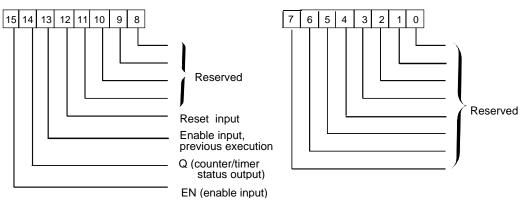

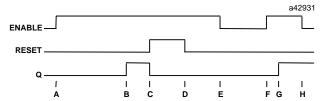

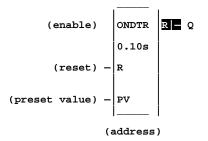

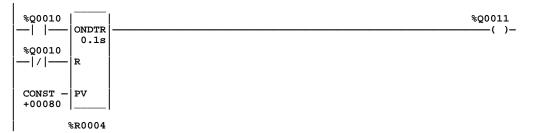

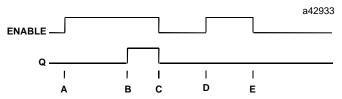

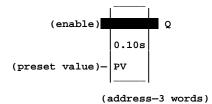

|           | ONDTR                                                    | 5-3 |

|           | Parameters                                               |     |

|           | Valid Memory Types                                       |     |

|           | Example                                                  | 5-5 |

|           | TMR                                                      | 5-5 |

|           | Parameters                                               | 5-6 |

|           | Valid Memory Types                                       | 5-6 |

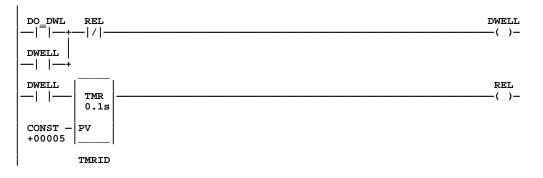

|           | Example                                                  | 5-7 |

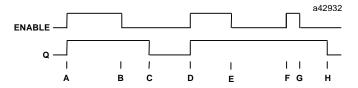

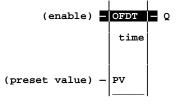

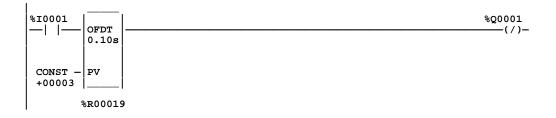

|           | OFDT                                                   |      |

|-----------|--------------------------------------------------------|------|

|           | Parameters                                             | 5-9  |

|           | Valid Memory Types                                     |      |

|           | Example                                                |      |

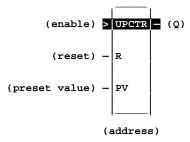

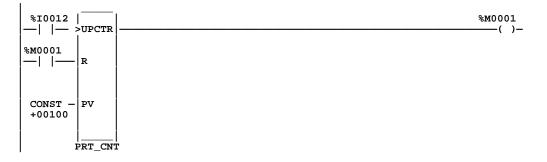

|           | UPCTR                                                  | 5-11 |

|           | Parameters                                             | 5-11 |

|           | Valid Memory Types                                     |      |

|           | Example                                                |      |

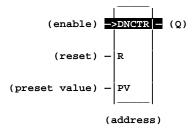

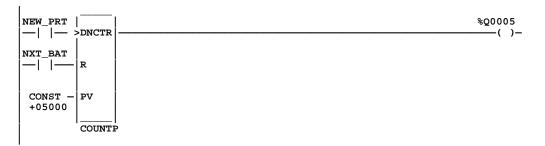

|           | DNCTR                                                  |      |

|           | Parameters                                             |      |

|           | Valid Memory Types                                     |      |

|           | Example                                                |      |

|           | Example                                                |      |

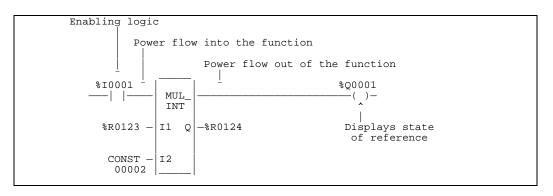

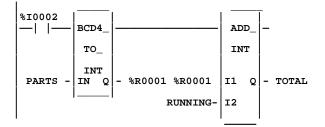

| Chapter 6 | Math Functions                                         | 6-1  |

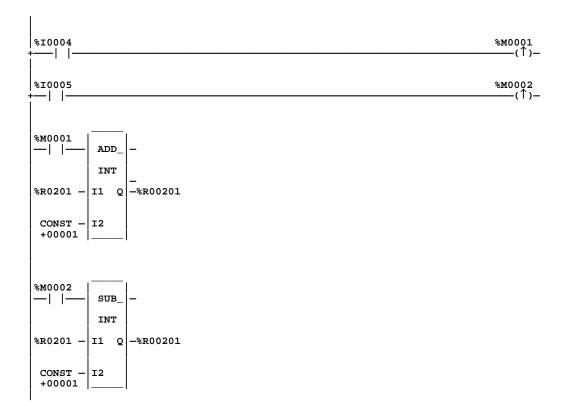

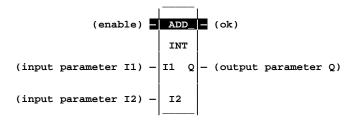

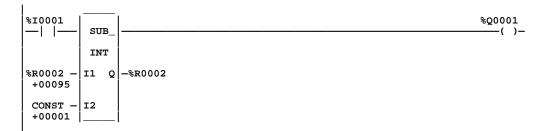

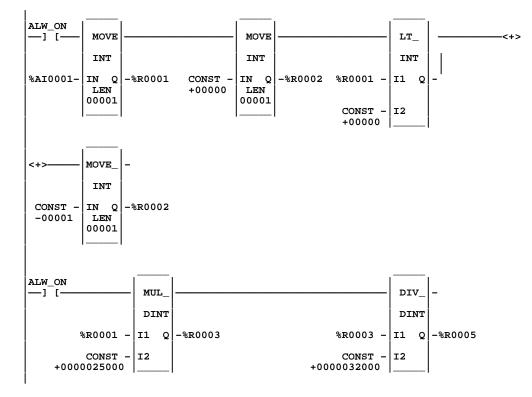

|           | Standard Math Functions (ADD, SUB, MUL, DIV)           |      |

|           | Parameters                                             |      |

|           | Valid Memory Types                                     | 6-3  |

|           | Example                                                | 6-3  |

|           | Math Functions and Data Types                          | 6-4  |

|           | Example                                                | 6-5  |

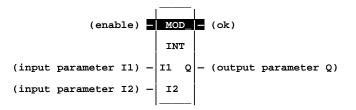

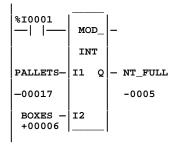

|           | MOD (INT, DINT)                                        | 6-6  |

|           | Parameters                                             | 6-6  |

|           | Valid Memory Types                                     | 6-7  |

|           | Example                                                | 6-7  |

|           | SQRT (INT, DINT, REAL)                                 | 6-8  |

|           | Parameters                                             | 6-8  |

|           | Valid Memory Types                                     | 6-9  |

|           | Example                                                | 6-9  |

|           | Trig Functions (SIN, COS, TAN, ASIN, ACOS, ATAN)       | 6-10 |

|           | Parameters                                             | 6-11 |

|           | Valid Memory Types                                     | 6-11 |

|           | Example                                                | 6-11 |

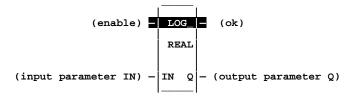

|           | Logarithmic/Exponential Functions (LOG, LN, EXP, EXPT) |      |

|           | Parameters                                             |      |

|           | Valid Memory Types                                     | 6-13 |

|           | Example                                                | 6-13 |

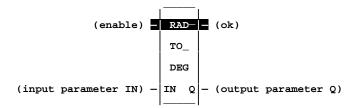

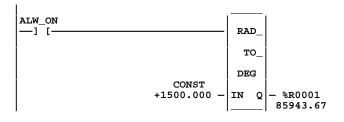

|           | Radian Conversion (RAD, DEG)                           | 6-14 |

|           | Parameters                                             | 6-14 |

|           | Valid Memory Types                                     | 6-14 |

|           | Example                                                | 6-15 |

|           |                                                        |      |

| Chapter 7 | Relational Functions                                   |     |

|-----------|--------------------------------------------------------|-----|

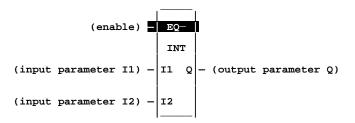

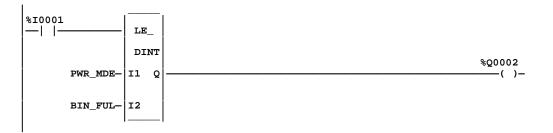

|           | Standard Relational Functions (EQ, NE, GT, GE, LT, LE) |     |

|           | Parameters                                             |     |

|           | Expanded Description                                   |     |

|           | Valid Memory Types                                     |     |

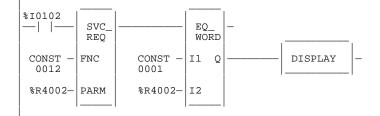

|           | Example                                                |     |

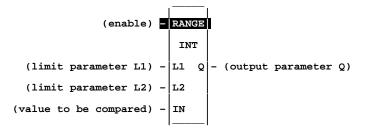

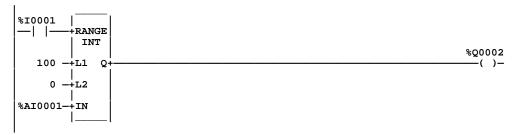

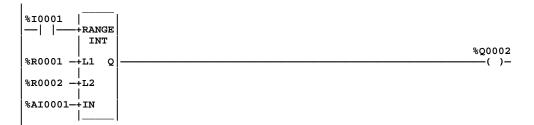

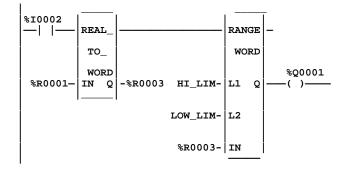

|           | RANGE (INT, DINT, WORD)                                |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example 1                                              |     |

|           | Example 2                                              | 7-6 |

| Chapter 8 | Bit Operation Functions                                |     |

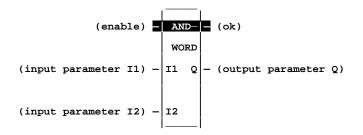

|           | AND and OR (WORD)                                      |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

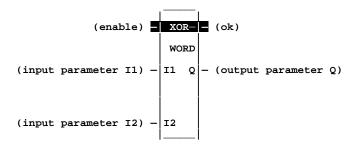

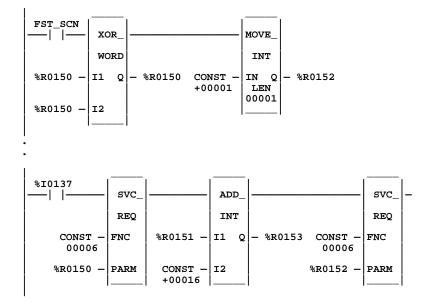

|           | XOR (WORD)                                             |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

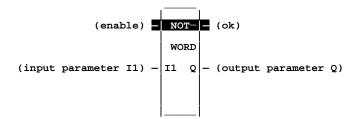

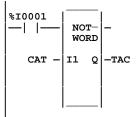

|           | NOT (WORD)                                             |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

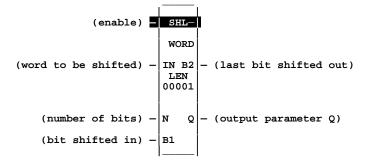

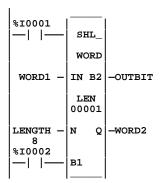

|           | SHL and SHR (WORD)                                     |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

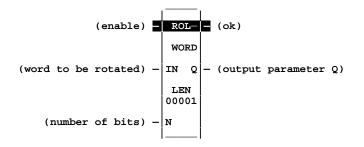

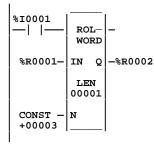

|           | ROL and ROR (WORD)                                     |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

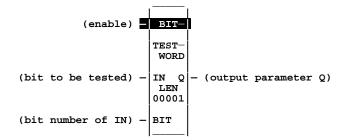

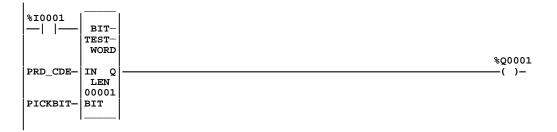

|           | BTST (WORD)                                            |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

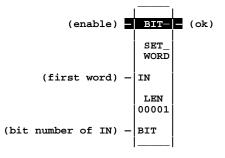

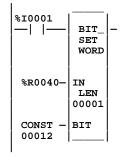

|           | BSET and BCLR (WORD)                                   |     |

|           | Parameters                                             |     |

|           | Valid Memory Types                                     |     |

|           | Example                                                |     |

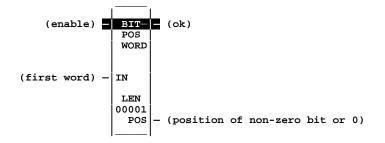

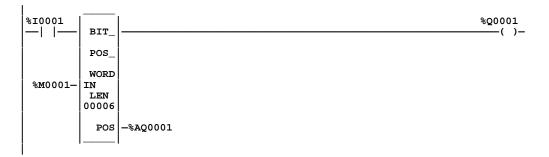

|           | BPOS (WORD)                                            |     |

|            | Parameters                              |      |

|------------|-----------------------------------------|------|

|            | Valid Memory Types                      |      |

|            | Example                                 |      |

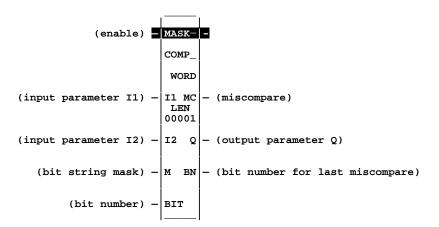

|            | MSKCMP (WORD, DWORD)                    |      |

|            | Parameters                              |      |

|            | Valid Memory Types                      |      |

|            | Example                                 |      |

| Chapter 9  | Data Move Functions                     |      |

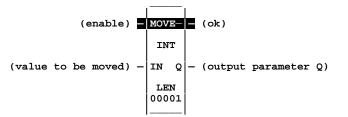

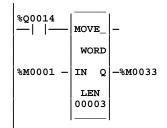

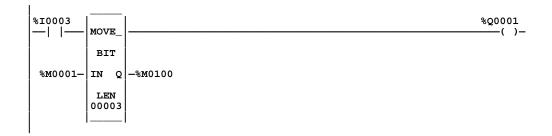

|            | MOVE (BIT, INT, WORD, REAL)             |      |

|            | Parameters                              |      |

|            | Example 1                               | 9-4  |

|            | Example 2                               | 9-4  |

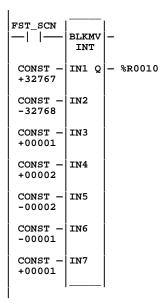

|            | BLKMOV (INT, WORD, REAL)                |      |

|            | Parameters                              |      |

|            | Valid Memory Types                      | 9-6  |

|            | Example                                 | 9-6  |

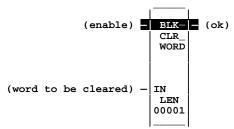

|            | BLKCLR (WORD)                           | 9-7  |

|            | Parameters                              | 9-7  |

|            | Valid Memory Types                      | 9-7  |

|            | Example                                 | 9-7  |

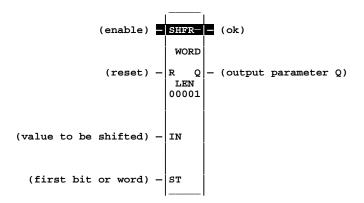

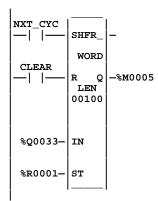

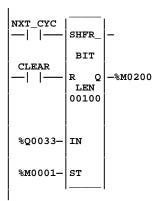

|            | SHFR (BIT, WORD)                        |      |

|            | Parameters                              | 9-9  |

|            | Valid Memory Types                      | 9-9  |

|            | Example 1                               |      |

|            | Example 2                               |      |

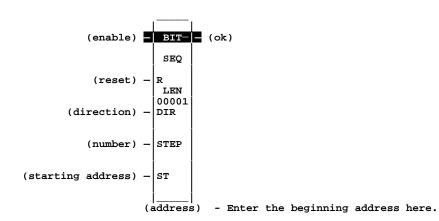

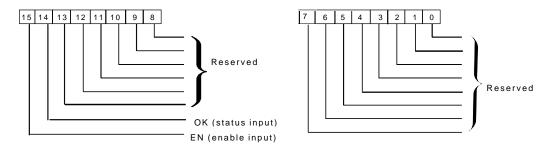

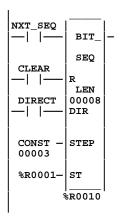

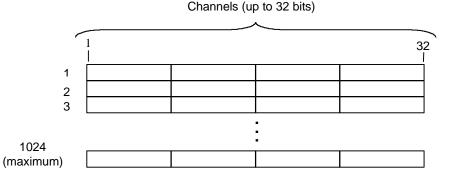

|            | BITSEQ (BIT)                            | 9-11 |

|            | Memory Required for a Bit Sequencer     | 9-11 |

|            | Parameters                              |      |

|            | Valid Memory Types                      |      |

|            | Example                                 |      |

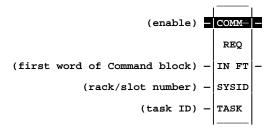

|            | COMMREQ                                 |      |

|            | Command Block                           |      |

|            | Parameters                              |      |

|            | Valid Memory Types                      |      |

|            | Example                                 |      |

| Chapter 10 | Table Functions                         | 10-1 |

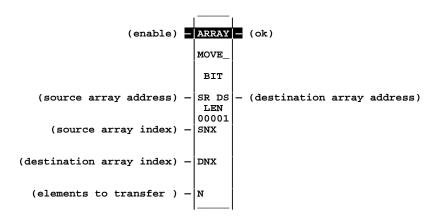

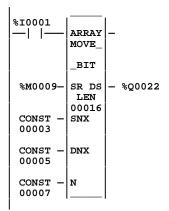

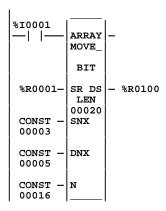

|            | ARRAY_MOVE (INT, DINT, BIT, BYTE, WORD) |      |

|            | Parameters                              |      |

|            | Valid Memory Types                      |      |

|            | Example 1                               |      |

|            | -                                       |      |

|            | Example 2                       |       |

|------------|---------------------------------|-------|

|            | Example 3                       |       |

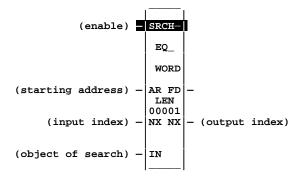

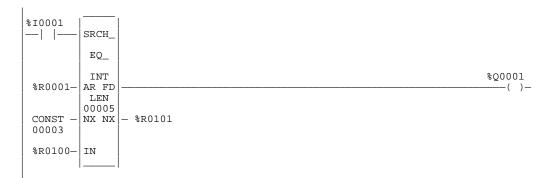

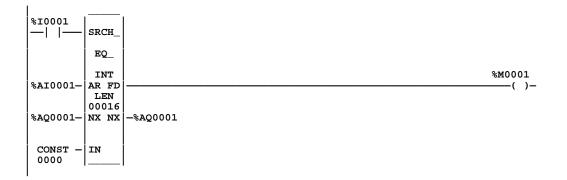

|            | Search Functions                |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

|            | Example 1                       |       |

|            | Example 2                       |       |

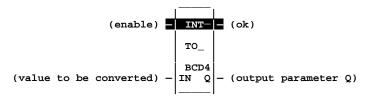

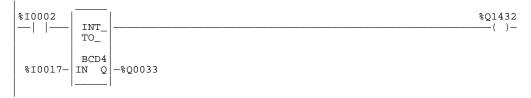

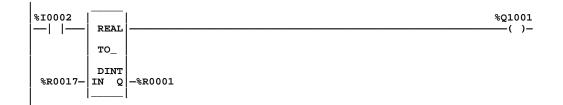

| Chapter 11 | Conversion Functions            |       |

|            | —>BCD-4 (INT)                   |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

|            | Example                         |       |

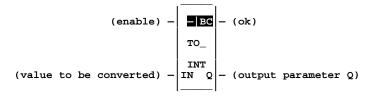

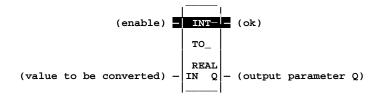

|            | —>INT (BCD-4, REAL)             |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

|            | Example                         |       |

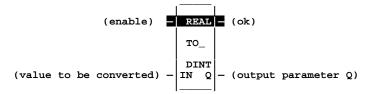

|            | —>DINT (REAL)                   |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

|            | Example                         | 11-6  |

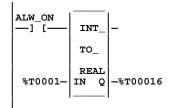

|            | —>REAL (INT, DINT, BCD-4, WORD) | 11-7  |

|            | Parameters                      | 11-7  |

|            | Valid Memory Types              | 11-7  |

|            | Example                         |       |

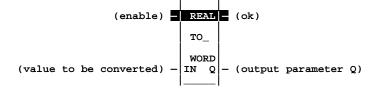

|            | —>WORD (REAL)                   |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

|            | Example                         |       |

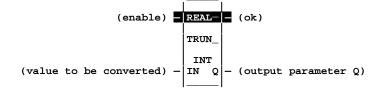

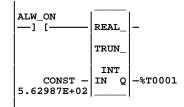

|            | TRUN (INT, DINT)                | 11-11 |

|            | Parameters                      | 11-11 |

|            | Valid Memory Types              | 11-11 |

|            | Example                         |       |

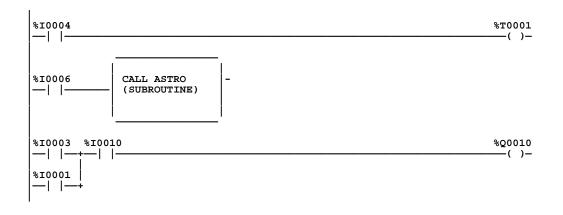

| Chapter 12 | Control Functions               | 12-1  |

|            | CALL                            |       |

|            | Example                         |       |

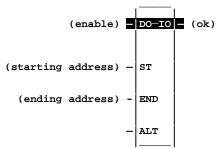

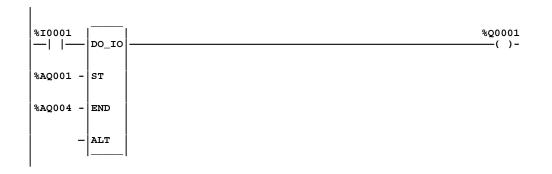

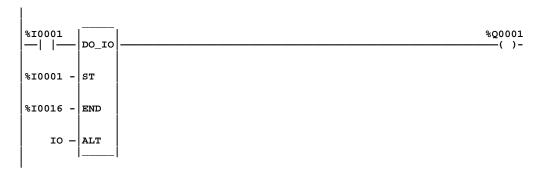

|            | DOIO                            |       |

|            | Parameters                      |       |

|            | Valid Memory Types              |       |

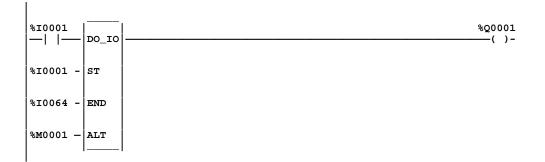

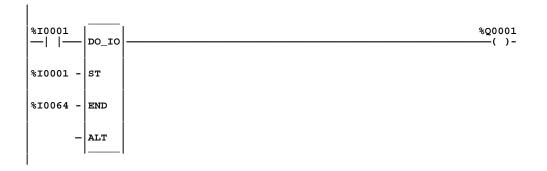

|            | Input Example 1                 |       |

|            | Input Example 2                 |       |

|            | × ×                             |       |

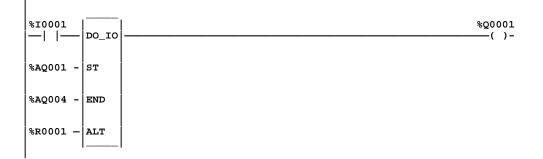

| Output Example 1                                                  | 12-6       |

|-------------------------------------------------------------------|------------|

| Output Example 2                                                  | 12-6       |

| Enhanced DO I/O Function for 331 and Later CPUs                   | 12-7       |

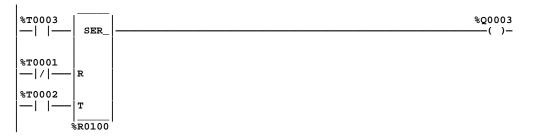

| SER                                                               | 12-8       |

| Features                                                          | 12-8       |

| Sample SER Function Block                                         | 12-8       |

| Parameters                                                        | 12-9       |

| Valid Memory Types                                                | 12-9       |

| Function Control Block                                            | 12-10      |

| Status Extra Data States                                          | 12-12      |

| SER Data Block Format                                             | 12-13      |

| SER Operation                                                     | 12-13      |

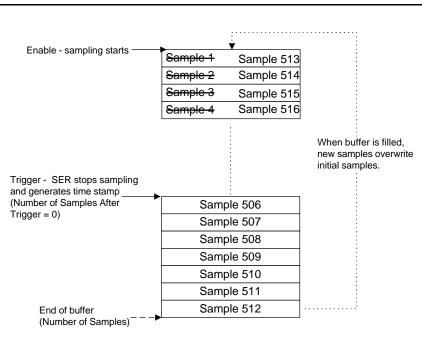

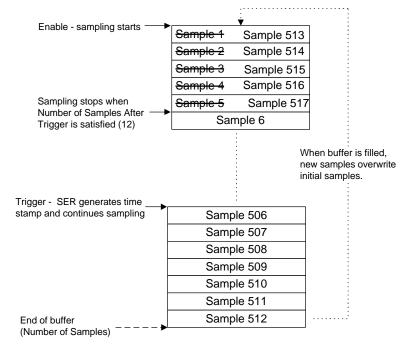

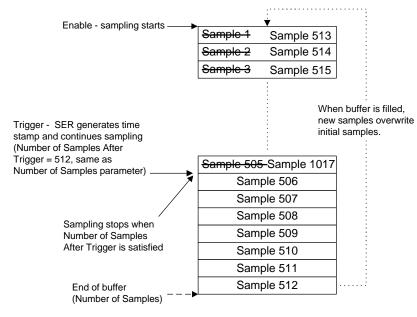

| Sampling Modes                                                    | 12-14      |

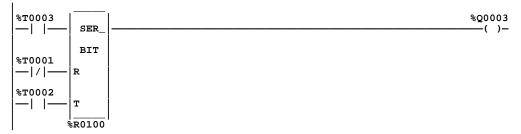

| SER Example                                                       | 12-16      |

| SER Function Block Trigger Timestamp Formats                      | 12-20      |

| END                                                               | 12-21      |

| Example                                                           | 12-21      |

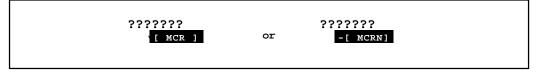

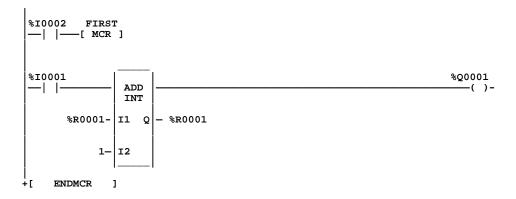

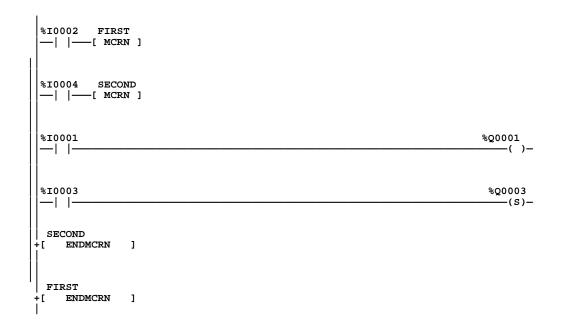

| MCRN/MCR                                                          | 12-22      |

| CPU Compatibility                                                 | 12-22      |

| MCRN Operation                                                    | 12-22      |

| MCR Operation                                                     | 12-23      |

| Parameters                                                        | 12-23      |

| Differences Between MCRs and JUMPs                                | 12-23      |

| Example                                                           | 12-24      |

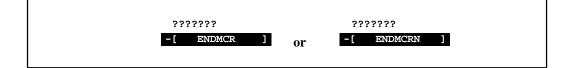

| ENDMCRN/ENDMCR                                                    | 12-25      |

| Example                                                           | 12-25      |

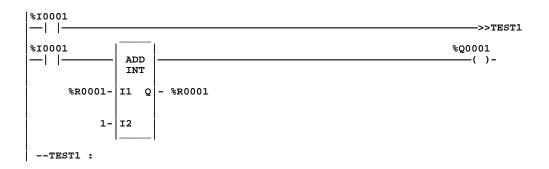

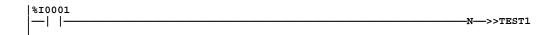

| JUMP                                                              | 12-26      |

| Examples                                                          | 12-27      |

| LABEL                                                             | 12-28      |

| Example                                                           | 12-28      |

| COMMENT                                                           | 12-29      |

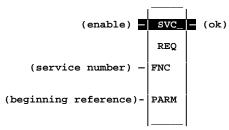

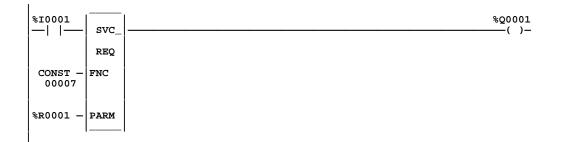

| SVCREQ                                                            | 12-30      |

| SVC REQ Overview                                                  | 12-31      |

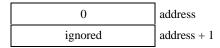

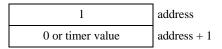

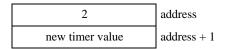

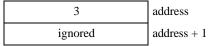

| SVCREQ #1: Change/Read Constant Sweep Timer                       | 12-33      |

| SVCREQ #2: Read Window Values                                     | 12-36      |

| SVCREQ #3: Change Programmer Communications Window Mode and Timer | Value12-38 |

| SVCREQ #4: Change System Comm Window Mode and Timer Value         | 12-40      |

| SVCREQ #6: Change/Read Number of Words to Checksum                | 12-42      |

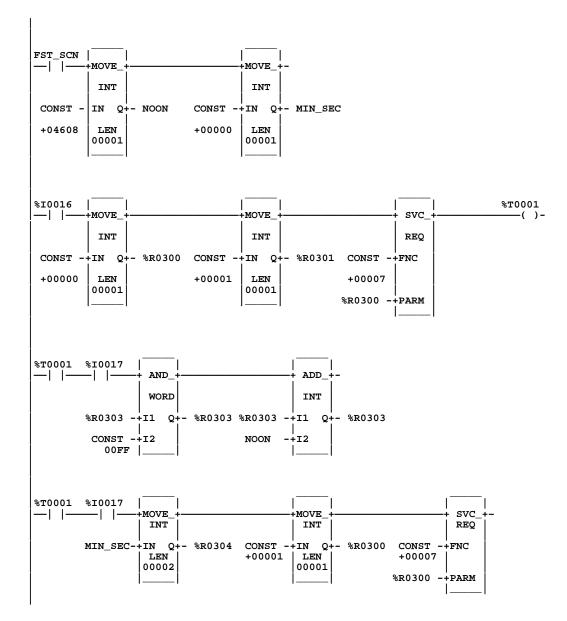

| SVCREQ #7: Change/Read Time-of-Day Clock                          | 12-44      |

| SVCREQ #8: Reset Watchdog Timer                                   | 12-48      |

| SVCREQ #9: Read Sweep Time from Beginning of Sweep                | 12-49      |

| SVCREQ #10: Read Folder Name                                      | 12-50      |

GFK-0467L

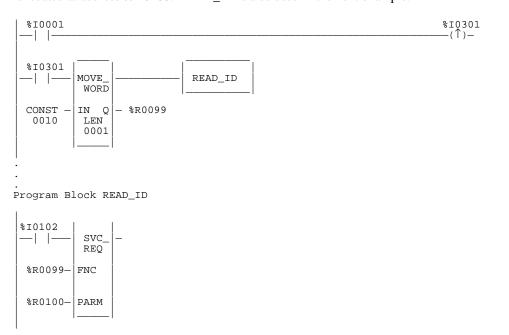

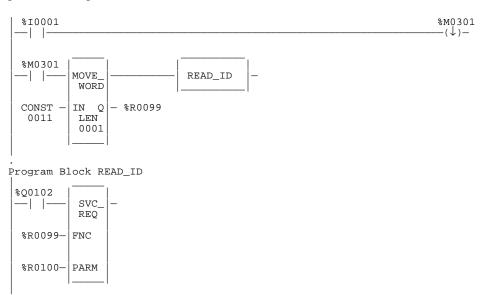

| SVCREQ #11: Read PLC ID                         |                         |

|-------------------------------------------------|-------------------------|

| SVCREQ #12: Read PLC Run State                  |                         |

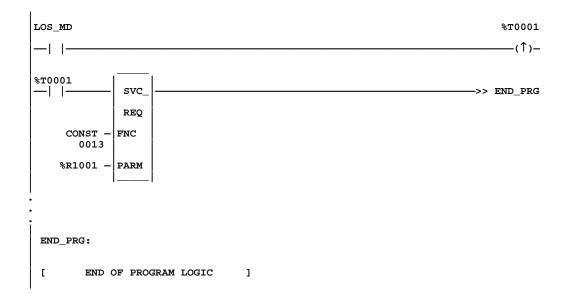

| SVCREQ #13: Shut Down (Stop) PLC                |                         |

| SVCREQ #14: Clear Fault Tables                  |                         |

| SVCREQ #15: Read Last-Logged Fault Table Entry  |                         |

| SVCREQ #16: Read Elapsed Time Clock             |                         |

| SVCREQ #18: Read I/O Override Status            |                         |

| SVCREQ #23: Read Master Checksum                |                         |

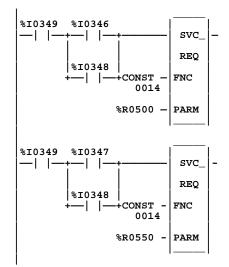

| SVCREQ #26/30: Interrogate I/O                  |                         |

| SVCREQ #29: Read Elapsed Power Down Time        |                         |

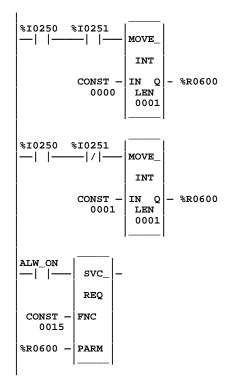

| SVCREQ #45: Skip Next Output & Input Scan       |                         |

| SVCREQ #46: Fast Backplane Status Access        |                         |

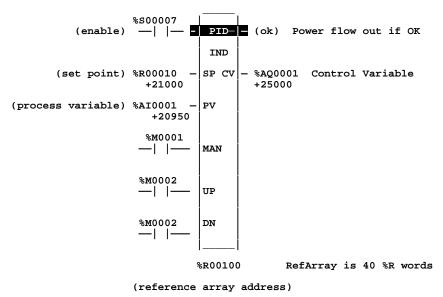

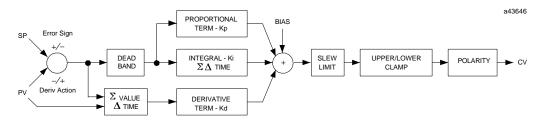

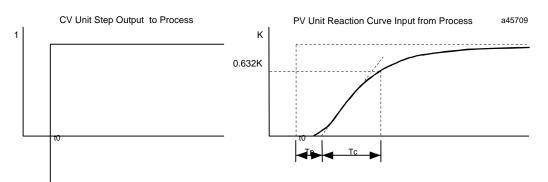

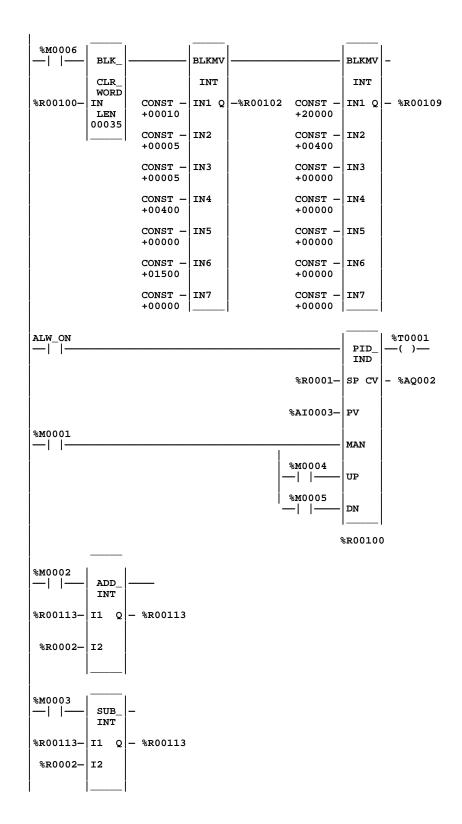

| PID                                             |                         |

| Parameters                                      |                         |

| Valid Memory Types                              |                         |

|                                                 |                         |

| Operation of the PID Instruction                |                         |

| Instruction Timing                              | A-1                     |

| Instruction Sizes for High Performance CPUs     | A-11                    |

| -                                               |                         |

| Interpreting Fault Tables                       | B-1                     |

| PLC Fault Table                                 | B-1                     |

|                                                 |                         |

| Instruction Mnemonics                           | C-1                     |

| Key Functions                                   | D-1                     |

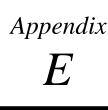

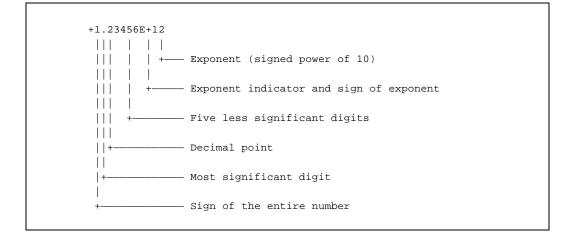

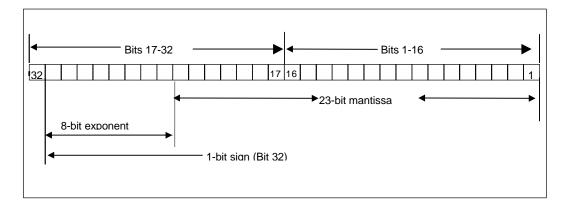

| Using Floating-Point Numbers                    | E-1                     |

| Floating-Point Numbers                          | E-1                     |

|                                                 |                         |

| e e                                             |                         |

|                                                 |                         |

| Errors in Floating-Point Numbers and Operations | E-6                     |

|                                                 | SVCREQ #11: Read PLC ID |

# Contents

| Figure 2-1. PLC Sweep                                   | 2-3  |

|---------------------------------------------------------|------|

| Figure 2-2. Programmer Communications Window Flow Chart |      |

| Figure 2-3. System Communications Window Flow Chart     | 2-11 |

| Figure 2-4. PCM Communications with the PLC             | 2-12 |

| Figure 2-5. Power-Up Sequence                           | 2-31 |

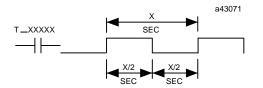

| Figure 2-6. Time-Tick Contact Timing Diagram            | 2-36 |

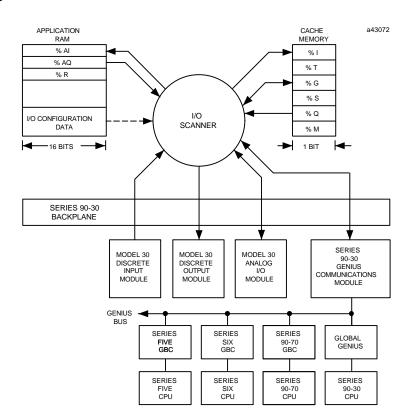

| Figure 2-7. Series 90-30 I/O Structure                  | 2-39 |

| Figure 2-8. Series 90-30 I/O Modules                    |      |

| Figure 12-1. Example of Pre-Trigger SER Sampling        |      |

| Figure 12-2. Example of Mid-Trigger SER Sampling        |      |

| Figure 12-3. Post-Trigger SER Sampling                  |      |

| Figure 12-4. Independent Term Algorithm (PIDIND)        |      |

| Table 2-1. Sweep Time Contribution                                                         | 2-4  |

|--------------------------------------------------------------------------------------------|------|

| Table 2-2. I/O Scan Time Contributions for the 90-30 35x and 36x Series (in milliseconds). | 2-5  |

| Table 2-3. I/O Scan Time Contributions for the 90-30 Series up to 341 (in milliseconds)    | 2-6  |

| Table 2-4. Register References                                                             |      |

| Table 2-5. Discrete References                                                             |      |

| Table 2-5. Discrete References - Continued                                                 |      |

| Table 2-6. Data Types                                                                      |      |

| Table 2-7. System Status References                                                        |      |

| Table 2-7. System Status References - Continued                                            |      |

| Table 2-7. System Status References - Continued                                            |      |

| Table 2-8. Series 90-30 I/O Modules                                                        |      |

| Table 2-8. Series 90-30 I/O Modules - Continued                                            | 2-41 |

| Table 2-8. Series 90-30 I/O Modules - Continued                                            |      |

| Table 3-1. Fault Summary                                                                   |      |

| Table 3-2. Fault Actions                                                                   |      |

| Table 4-1. Types of Contacts                                                               | 4-1  |

| Table 4-2. Types of Coils                                                                  |      |

| Table 12-1. Function Control Block for SER Example                                         |      |

| Table 12-2. Sample Contents for SER Example                                                |      |

| Table 12-3. Data Block for SER Control Block Example                                       |      |

| Table 12-4. Service Request Functions                                                      |      |

| Table 12-5. Output Values for Read Extra Data Function                                     |      |

| Table 12-6. Output Values for Write Data Function                                          |      |

| Table 12-7. Output Values for Read/Write Data Function                                     |      |

| Table 12-8. PID Parameters Overview                                                        |      |

| Table 12-8. PID Parameters Overview - Continued                                            |      |

| Table 12-9. PID Parameter Details                                                          |      |

| Table 12-9. PID Parameter Details - Continued                                              |      |

| Table 12-9. PID Parameter Details - Continued                                              |      |

| Table A-1. Instruction Timing, Standard Models                                             | A-2  |

| Table A-1. Instruction Timing, Standard Models-Continued                                   | A-3  |

| Table A-1. Instruction Timing, Standard Models-Continued                                   | A-4  |

| Table A-1. Instruction Timing, Standard Models-Continued                                   | A-5  |

| Table A-2. Instruction Timing, High Performance Models                                     | A-6  |

| Table A-2. Instruction Timing, High Performance Models-Continued                           | A-7  |

| Table A-2. Instruction Timing, High Performance Models-Continued                           | A-8  |

# Contents

| Table A-2. | Instruction Timing, High Performance Models-Continued    | A-9  |

|------------|----------------------------------------------------------|------|

| Table A-3. | SER Function Block Timing                                | A-10 |

| Table A-4. | Instruction Sizes for 350—352, 360, 363, and 364 CPUs    | A-11 |

| Table B-1. | PLC Fault Groups                                         | B-4  |

| Table B-2. | PLC Fault Actions                                        | B-5  |

| Table B-3. | Alarm Error Codes for PLC CPU Software Faults            | B-5  |

| Table B-4. | Alarm Error Codes for PLC Faults                         | B-6  |

| Table B-5. | PLC Fault Data - Illegal Boolean Opcode Detected         | B-7  |

| Table B-6. | PLC Fault Time Stamp                                     | B-7  |

| Table B-7. | I/O Fault Table Format Indicator Byte                    | B-9  |

| Table B-8. | I/O Reference Address                                    | B-9  |

|            | I/O Reference Address Memory Type                        |      |

| Table B-10 | ). I/O Fault Groups                                      | B-10 |

|            | . I/O Fault Actions                                      |      |

| Table B-12 | 2. I/O Fault Specific Data                               | B-11 |

| Table B-13 | 3. I/O Fault Time Stamp                                  | B-12 |

| Table E-1. | General Case of Power Flow for Floating-Point Operations | E-7  |

# Chapter 1

# Introduction

The Series 90-30, 90-20, and Micro PLCs are members of the GE Fanuc Series 90 family of Programmable Logic Controllers (PLCs). They are easy to install and configure, offer advanced programming features, and are compatible with the Series 90-70 PLCs.

The Series 90-20 PLC provides a cost-effective platform for low I/O count applications. The primary objectives of the Series 90-20 PLC are as follows:

- To provide a small PLC that is easy to use, install, upgrade, and maintain.

- To provide a cost-effective family-compatible PLC.

- To provide easier system integration through standard communication hardware and protocols.

The Series 90 Micro PLC also provides a cost-effective platform for lower I/O count applications. The primary objectives of the Micro PLC are the same as those for the Series 90-20. In addition, the Micro offers the following:

- The Micro PLC has the CPU, power supply, inputs and outputs all built into one small device.

- Most models also have a high speed counter.

- Because the CPU, power supply, inputs and outputs all built into one device, it is very easy to configure.

The software structure for the 341 and lower Series 90-30 PLCs and Series 90-20 PLC uses an architecture that manages memory and execution priority in the 80188 microprocessor. The 35x and 36x series of 90-30 PLCs use an 80386EX microprocessor. The Series 90 Micro PLC uses the H8 microprocessor. This operation supports both program execution and basic housekeeping tasks such as diagnostic routines, input/output scanners, and alarm processing. The system software also contains routines to communicate with the programmer. These routines provide for the upload and download of application programs, return of status information, and control of the PLC.

In the Series 90-30 PLC, the application (user logic) program that controls the end process to which the PLC is applied is controlled by a dedicated Instruction Sequencer Coprocessor (ISCP). The ISCP is implemented in hardware in the Model 313 and higher and in software in the Model 311 systems, and the Micro PLC. The 80188 microprocessor and the ISCP can execute simultaneously, allowing the microprocessor to service communications while the ISCP is executing the bulk of the application program; however, the microprocessor must execute the non-Boolean function blocks.

Faults occur in the Series 90-30 PLC, Series 90-20 PLC, and the Micro PLC when certain failures or conditions happen that affect the operation and performance of the system. These conditions may affect the ability of the PLC to control a machine or process. Other conditions may only act as an alert, such as a low battery signal to indicate that the voltage of the battery protecting the memory is low and should be replaced. The condition or failure is called a fault.

Faults are handled by a software alarm processor function that records the faults in either the PLC fault table or the I/O fault table. (Model 331 and higher CPUs also time-stamp the faults.) These tables can be displayed through the programming software on the PLC Fault Table and I/O Fault Table screens in Logicmaster 90-30/20/Micro software using the control and status functions.

#### Note

Floating-point capabilities are *only* supported on the 35x and 36x series CPUs, Release 9 or later, and on all releases of CPU352.

The Model 364 CPU (release 9.10 or later) is the only Series 90-30 CPU that supports EGD.

#### Note

For additional information, see the appendices in the back of this manual.

- Appendix A lists the memory size in bytes and the execution time in microseconds for each programming instruction.

- Appendix B describes how to interpret the message structure format when reading the PLC and I/O fault tables.

- Appendix C lists instruction mnemonics for searching or editing a program.

- Appendix D lists the special keyboard assignments used in the Logicmaster 90-30/20/Micro Software.

- Appendix E describes the use of floating-point math operations.

# Chapter System Operation

This chapter describes certain system operations of the Series 90-30, 90-20, and Micro PLC systems. These system operations include:

| • | A summary of PLC sweep sequences (Section 1)              | 2-2    |

|---|-----------------------------------------------------------|--------|

| • | Program organization and user references/data (Section 2) | . 2-17 |

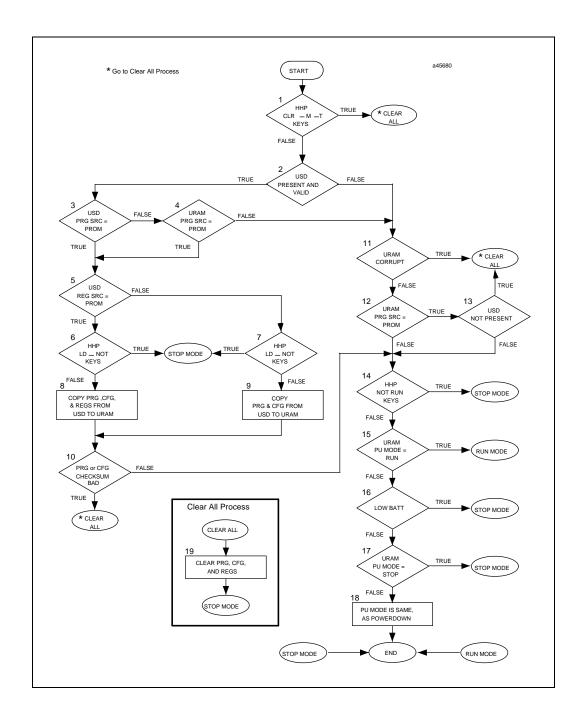

| • | Power-up and power-down sequences (Section 3)             | . 2-30 |

| • | Clocks and timers (Section 4)                             | . 2-34 |

| • | System security through password assignment (Section 5)   | . 2-37 |

| • | Series 90-30 I/O modules (Section 6)                      | . 2-39 |

# Section 1: PLC Sweep Summary

The logic program in the Series 90-30, 90-20, and Micro PLCs execute repeatedly until stopped by a command from the programmer or a command from another device. The sequence of operations necessary to execute a program one time is called a sweep. In addition to executing the logic program, the sweep includes obtaining data from input devices, sending data to output devices, performing internal housekeeping, servicing the programmer, and servicing other communications.

Series 90-30, 90-20, and Micro PLCs normally operate in **STANDARD PROGRAM SWEEP** mode. Other operating modes include **STOP WITH I/O DISABLED** mode, **STOP WITH I/O ENABLED** mode, and **CONSTANT SWEEP** mode. Each of these modes, described in this chapter, is controlled by external events and application configuration settings. The PLC makes the decision regarding its operating mode at the start of every sweep.

# Standard Program Sweep

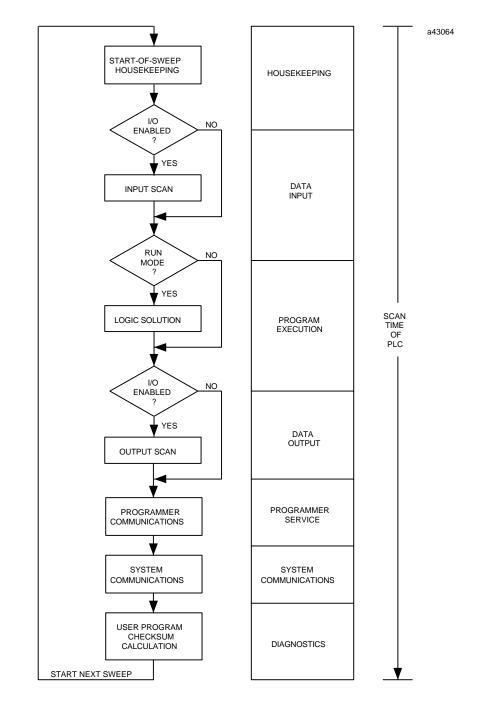

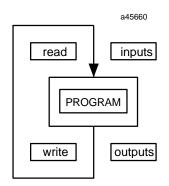

**STANDARD PROGRAM SWEEP** mode normally runs under all conditions. The CPU operates by executing an application program, updating I/O, and performing communications and other tasks. This occurs in a repetitive cycle called the CPU sweep. There are seven parts to the execution sequence of the Standard Program Sweep:

- 1. Start-of-sweep housekeeping

- 2. Input scan (read inputs)

- 3. Application program logic solution

- 4. Output scan (update outputs)

- 5. Programmer service

- 6. Non-programmer service

- 7. Diagnostics

All of these steps execute every sweep. Although the Programmer Communications Window opens each sweep, programmer services only occur if a board fault has been detected or if the programming device issues a service request; that is, the Programmer Communications Window first checks for work to do and exits if there is none. The sequence of the standard program sweep is shown in the following figure.

Figure 2-1. PLC Sweep

As shown in the PLC sweep sequence, several items are included in the sweep. These items contribute to the total sweep time as shown in the following table.

| Sweep<br>Element            | 1 1                                                                                                                                                                                            |                  | Time Contribution (ms) <sup>4</sup>                                                                                                                                         |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                             |                                                                                                                                                                                                |                  | 351, 352, 350, and 36x series (times for 350 and 36x series estimated to be the same)                                                                                       |  |  |

| Housekeeping                | <ul> <li>Calculate sweep time.</li> <li>Schedule start of next sweep.</li> <li>Determine mode of next sweep.</li> <li>Update fault reference tables.</li> <li>Reset watchdog timer.</li> </ul> |                  | 0.279                                                                                                                                                                       |  |  |

| Data Input                  | Input data is received from input and option modules.                                                                                                                                          |                  | See Table 2-2 for scan time contributions.                                                                                                                                  |  |  |

| Program<br>Execution        | User logic is solved.                                                                                                                                                                          |                  | Execution time is dependent upon the length of the program<br>and the type of instructions used in the<br>program. Instruction execution times are listed in<br>Appendix A. |  |  |

| Data Output                 | Output data is sent to output and option modules.                                                                                                                                              |                  | See Table 2-2 for scan time contributions.                                                                                                                                  |  |  |

| Service External<br>Devices | Service requests from HHP<br>programming devices and<br>intelligent modules are<br>processed. <sup>1</sup>                                                                                     |                  | 0.334                                                                                                                                                                       |  |  |

|                             |                                                                                                                                                                                                | LM-90            | 0.517                                                                                                                                                                       |  |  |

|                             |                                                                                                                                                                                                | PCM <sup>2</sup> | 0.482                                                                                                                                                                       |  |  |

| Reconfiguration             | Slots with faulted modules and empty slots are monitored.                                                                                                                                      |                  | 0.319 <sup>6</sup>                                                                                                                                                          |  |  |

| Diagnostics                 | Verify user program integrity                                                                                                                                                                  |                  | 0.010 per word checksummed each sweep <sup>3, 7</sup>                                                                                                                       |  |  |

Table 2-1. Sweep Time Contribution

The scan time contribution of external device service is dependent upon the mode of the communications window in which the service is processed. If the window mode is LINITED, a maximum of 8 milliseconds for the 311, 313, 323, and 331 CPUs and 6 milliseconds for the 340 and higher CPUs will be spent during that window. If the window mode is RUN-TO-COMPLETION, a maximum of 50 ms can be spent in that window, depending upon the number of requests which are presented simultaneously.

2. These measurements were taken with the PCM physically present but not configured and with no application task running on the PCM.

- 3. The number of words checksummed each sweep can be changed with the SVCREQ function block.

- 4. These measurements were taken with an empty program and the default configuration. The Series 90-30 PLCs were in an empty 10-slot rack with no extension racks connected. Also, the times in this table assume that there is no periodic subroutine active; the times will be larger if a periodic subroutine is active.

- 5. The data input time for the Micro PLC can be determined as follows: 0.365 ms. (fixed scan) + 0.036 ms. (filter time) x (total sweep time)/0.5 ms.

- 6. Since the Micro PLC has a static set of I/O, reconfiguration is not necessary.

- 7. Since the user program for the Micro PLC is in Flash memory, it will not be checked for integrity.

|                                           |                                           | 35x and 36x Series CPUs |                   |                |  |

|-------------------------------------------|-------------------------------------------|-------------------------|-------------------|----------------|--|

| Modu                                      | le Type                                   | Main<br>Rack            | Expansion<br>Rack | Remote<br>Rack |  |

| 8-point discrete inp                      | out                                       | .030                    | .055              | .206           |  |

| 16-point discrete in                      | put                                       | .030                    | .055              | .206           |  |

| 32-point discrete in                      | put                                       | .043                    | .073              | .269           |  |

| 8-point discrete out                      | put                                       | .030                    | .053              | .197           |  |

| 16-point discrete or                      | utput                                     | .030                    | .053              | .197           |  |

| 32-point discrete or                      | utput                                     | .042                    | .070              | .259           |  |

| Combination discre                        | ete input/output                          | .060                    | .112              | .405           |  |

| 4-channel analog ir                       | nput                                      | .075                    | .105              | .396           |  |

| 2-channel analog o                        | utput                                     | .058                    | .114              | .402           |  |

| 16-channel analog<br>(current or voltage) | 1                                         | .978                    | 1.446             | 3.999          |  |

| 8-channel analog o                        | utput                                     | 1.274                   | 1.988             | 4.472          |  |

| Combination analo                         | g input/output                            | 1.220                   | 1.999             | 4.338          |  |

| High Speed Counter                        | er                                        | 1.381                   | 2.106             | 5.221          |  |

| I/O Processor                             |                                           | 1.574                   | 2.402             | 6.388          |  |

| Ethernet Interface (                      | no connection)                            | .038                    | .041              | .053           |  |

| Power Mate APM                            | (1-axis)                                  | 1.527                   | 2.581             | 6.388          |  |

| Power Mate APM                            | (2-axis)                                  | 1.807                   | 2.864             | 7.805          |  |

| DSM 302 *                                 | 40 AI, 6 AQ                               | 2.143                   | 3.315             | 9.527          |  |

|                                           | 50AI, 9 AQ                                | 2.427                   | 3.732             | 11.092         |  |

|                                           | 64 AI, 12 AQ                              | 2.864                   | 4.317             | 13.138         |  |

| GCM                                       | no devices                                | .911                    | 1.637             | 5.020          |  |

|                                           | 8 64-word devices                         | 8.826                   | 16.932            | 21.179         |  |

| GCM+                                      | no devices                                | .567                    | .866              | 1.830          |  |

|                                           | 32 64-word devices                        | 1.714                   | 2.514             | 5.783          |  |

| GBC                                       | no devices                                | .798                    | 1.202             | 2.540          |  |

|                                           | 32 64-word devices                        | 18.382                  | 25.377            | 70.777         |  |

| PCM 311                                   | not configured, or<br>no application task | .476                    | N/A               | N/A            |  |

| read 128 %R as<br>fast as possible        |                                           | .485                    | N/A               | N/A            |  |

| ADC (no task)                             |                                           | .476                    | N/A               | N/A            |  |

| I/O Link Master                           |                                           |                         | .865              | 1.932          |  |

|                                           | 16 64-point<br>devices                    | 4.948                   | 7.003             | 19.908         |  |

| I/O Link Slave                            | 32-point                                  | .087                    | .146              | .553           |  |

|                                           | 64-point                                  |                         | .213              | .789           |  |

Table 2-2. I/O Scan Time Contributions for the 90-30 35x and 36x Series (in milliseconds)

\* For applications where the DSM's contributions to scan time will affect machine operation you may need to use the Do I/O function block, and the Suspend I/O and Fast Backplane Status Access service requests to transfer necessary data to and from the Motion module without getting all the data every scan. Refer to the *Motion Mate DSM302 for Series 90-30 PLCs User's Manual*, GFK1464 for details.

|                                                 |                                           | CPU Model |              |                   |                |              |                   |                |

|-------------------------------------------------|-------------------------------------------|-----------|--------------|-------------------|----------------|--------------|-------------------|----------------|

| Module Type                                     |                                           | 331       |              |                   |                | 340/341      |                   |                |

|                                                 |                                           | 311/313   | Main<br>Rack | Expansion<br>Rack | Remote<br>Rack | Main<br>Rack | Expansion<br>Rack | Remote<br>Rack |

| 8-point discrete                                | input                                     | .076      | .054         | .095              | .255           | .048         | .089              | .249           |

| 16-point discret                                | e input                                   | .075      | .055         | .097              | .257           | .048         | .091              | .250           |

| 32-point discret                                | e input                                   | .094      | .094         | .126              | .335           | .073         | .115              | .321           |

| 8-point discrete                                | output                                    | .084      | .059         | .097              | .252           | .053         | .090              | .246           |

| 16-point discret                                | e output                                  | .083      | .061         | .097              | .253           | .054         | .090              | .248           |

| 32-point discret                                | e output                                  | .109      | .075         | .129              | .333           | .079         | .114              | .320           |

| 8-point combina                                 | ation input/output                        | .165      | .141         | .218              | .529           | .098         | .176              | .489           |

| 4-channel analo                                 | g input                                   | .151      | .132         | .183              | .490           | .117         | .160              | .462           |

| 2-channel analo                                 | g output                                  | .161      | .138         | .182              | .428           | .099         | .148              | .392           |

| High-Speed Cou                                  | unter                                     | 2.070     | 2.190        | 2.868             | 5.587          | 1.580        | 2.175             | 4.897          |

| Power Mate AP                                   | M (1-axis)                                | 2.330     | 2.460        | 3.175             | 6.647          | 1.750        | 2.506             | 5.899          |

| Power Mate AP                                   | M (2-axis)                                | 3.181     | 3.647        | 4.497             | 9.303          | 2.154        | 3.097             | 7.729          |

| DSM 302                                         | 40 AI, 6 AQ                               | 3.613     | 4.081        | 5.239             | 11.430         | 2.552        | 3.648             | 9.697          |

|                                                 | 50AI, 9 AQ                                | 4.127     | 4.611        | 5.899             | 13.310         | 2.911        | 4.170             | 11.406         |

|                                                 | 64 AI, 12 AQ                              | 4.715     | 5.276        | 6.759             | 15.747         | 3.354        | 4.840             | 13.615         |

| GCM                                             | no devices                                | .041      | .054         | .063              | .128           | .038         | .048              | .085           |

|                                                 | 8 64-point devices                        | 11.420    | 11.570       | 13.247            | 21.288         | 9.536        | 10.648            | 19.485         |

| GCM+                                            | no devices                                | .887      | .967         | 1.164             | 1.920          | .666         | .901              | 1.626          |

|                                                 | 32 64-point<br>devices                    | 4.120     | 6.250        | 8.529             | 21.352         | 5.043        | 7.146             | 20.052         |

| PCM 311                                         | not configured, or<br>no application task | N/A       | 3.350        | N/A               | N/A            | 1.684        | N/A               | N/A            |

|                                                 | read 128 %R as fast as possible           | N/A       | 4.900        | N/A               | N/A            | 2.052        | N/A               | N/A            |

| ADC 311                                         |                                           | N/A       | 3.340        | N/A               | N/A            | 1.678        | N/A               | N/A            |

| 16-channel analog input<br>(current or voltage) |                                           | 1.370     | 1.450        | 1.937             | 4.186          | 1.092        | 1.570             | 3.796          |

| I/O Link                                        | no devices                                | 1.910     | 2.030        | 1.169             | 1.925          | .678         | .904              | 1.628          |

| Master                                          | sixteen 64-point<br>devices               | 6.020     | 6.170        | 8.399             | 21.291         | 4.992        | 6.985             | 20.010         |

| I/O Link Slave                                  | 32-point                                  | .206      | .222         | .289              | .689           | .146         | .226              | .636           |

|                                                 | 64-point                                  | .331      | .350         | .409              | 1.009          | .244         | .321              | .926           |

Table 2-3. I/O Scan Time Contributions for the 90-30 Series up to 341 (in milliseconds)

\* For applications where the DSM's contributions to scan time will affect machine operation you may need to use the Do I/O function block, and the Suspend I/O and Fast Backplane Status Access service requests to transfer necessary data to and from the Motion module without getting all the data every scan. Refer to the *Motion Mate DSM302 for Series 90-30 PLCs User's Manual*, GFK1464 for details.

#### Sweep Time Calculation

Table 2-1 lists the seven items that contribute to the sweep time of the PLC. The sweep time consists of fixed times (housekeeping and diagnostics) and variable times. Variable times vary according to the I/O configuration, size of the user program, and the type of programming device connected to the PLC.

#### **Example of Sweep Time Calculation**

An example of the calculations for determining the sweep time for a Series 90-30 model 331 PLC are shown in the table shown below.

The modules and instructions used for these calculations are listed below:

- Input modules: five 16-point Series 90-30 input modules.

- Output modules: four 16-point Series 90-30 output modules.

- Programming instructions: A 1200-step program consisting of 700 Boolean instructions (LD, AND, OR, etc.), 300 output coils (OUT, OUTM, etc.), and 200 math functions (ADD, SUB, etc.).

#### Housekeeping

The housekeeping portion of the sweep performs all of the tasks necessary to prepare for the start of the sweep. If the PLC is in **CONSTANT SWEEP** mode, the sweep is delayed until the required sweep time elapses. If the required time has already elapsed, the OV\_SWP %SA0002 contact is set, and the sweep continues without delay. Next, timer values (hundredths, tenths, and seconds) are updated by calculating the difference from the start of the previous sweep and the new sweep time. In order to maintain accuracy, the actual start of sweep is recorded in 100 microsecond increments. Each timer has a remainder field which contains the number of 100 microsecond increments that have occurred since the last time the timer value was incremented.

#### Input Scan

Scanning of inputs occurs during the input scan portion of the sweep, just prior to the logic solution. During this part of the sweep, all Series 90-30 input modules are scanned and their data stored in %I (discrete inputs) or %AI (analog inputs) memory, as appropriate. Any global data input received by a Genius Communications Module, an Enhanced Genius Communications Module, or a Genius Bus Controller is stored in %G memory.

Modules are scanned in ascending reference address order, starting with the Genius Communications Module, then discrete input modules, and finally analog input modules.

If the CPU is in **STOP** mode and the CPU is configured to not scan I/O in **STOP** mode, the input scan is skipped.

#### **Application Program Logic Scan or Solution**

The application program logic scan is when the application logic program actually executes. The logic solution always begins with the first instruction in the user application program immediately following the completion of the input scan. Solving the logic provides a new set of outputs. The logic solution ends when the END instruction is executed (the END is invisible unless you are using a Hand-Held Monitor).

The application program is executed by the ISCP and the 80C188 microprocessor. In the 313 and higher CPUs, the ISCP executes the Boolean instructions; and the 80C188 or 80386EX executes the timer, counter, and function blocks. In the Model 311 and 90-20 CPUs, the 80C188 executes all Boolean, timer, counter, and function block instructions. On the Micro, the H8 processor executes all Boolean and function blocks.

A list of execution times for each programming function can be found in Appendix A.

#### **Output Scan**

Outputs are scanned during the output scan portion of the sweep, immediately following the logic solution. Outputs are updated using data from %Q (for discrete outputs) and %AQ (for analog outputs) memory, as appropriate. If the Genius Communications Module is configured to transmit global data, then data from %G memory is sent to the GCM, GCM+, or GBC. The Series 90-20 and Micro output scans include discrete outputs only.

During the output scan, all Series 90-30 output modules are scanned in ascending reference address order.

If the CPU is in the **STOP** mode and the CPU is configured to not scan I/O during **STOP** mode, the output scan is skipped. The output scan is completed when all output data has been sent to all Series 90-30 output modules.

#### Logic Program Checksum Calculation

A checksum calculation is performed on the user program at the end of every sweep. Since it would take too long to calculate the checksum of the entire program, you can specify the number of words from 0 to 32 to be checked on the CPU detail screen.

If the calculated checksum does not match the reference checksum, the program checksum failure exception flag is raised. This causes a fault entry to be inserted into the PLC fault table and the PLC mode to be changed to **STOP**. If the checksum calculation fails, the programmer communications window is not affected. The default number of words to be checksummed is 8.

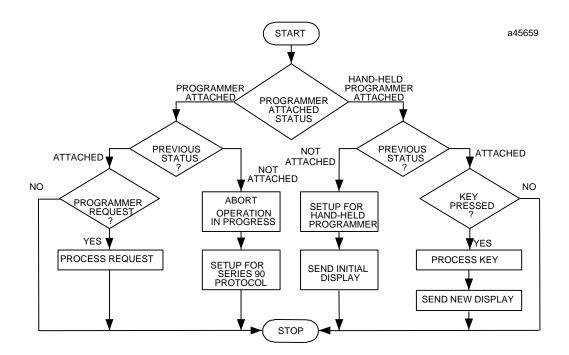

# **Programmer Communications Window**

This part of the sweep is dedicated to communicating with the programmer. If there is a programmer attached, the CPU executes the programmer communications window. The programmer communications window will not execute if there is no programmer attached and no board to be configured in the system. Only one board is configured each sweep.

Support is provided for the Hand-Held Programmer and for other programmers that can connect to the serial port and use the Series Ninety Protocol (SNP) protocol. Support is also provided for programmer communications with intelligent option modules.

In the default limited window mode, the CPU performs one operation for the programmer each sweep, that is, it honors one service request or response to one key press. If the programmer makes a request that requires more than 6 (or 8 depending on the CPU—see Note) milliseconds to process, the request processing is spread out over several sweeps so that no sweep is impacted by more than 6 (or 8 depending on the CPU—see Note) milliseconds.

#### Note

The time limit for the communications window is 6 milliseconds for the 340 and higher CPUs and 8 milliseconds for the 311, 313, 323, and 331 models.

The following figure is a flow chart for the programmer communications portion of the sweep.

Figure 2-2. Programmer Communications Window Flow Chart

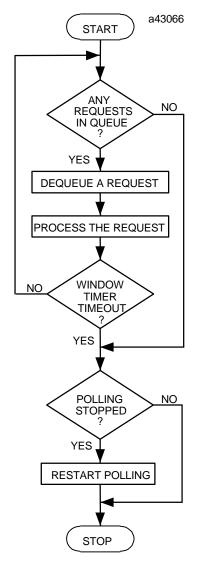

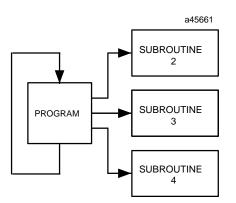

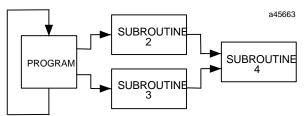

# System Communications Window

This is the part of the sweep where communications requests from intelligent option modules, such as the PCM or DSM, are processed (see flow chart). Requests are serviced on a first-come-first-served basis. However, since intelligent option modules are polled in a round-robin fashion, no intelligent option module has priority over any other intelligent option module.

In the default **Run-to-Completion** mode, the length of the system communications window is limited to 50 milliseconds. If an intelligent option module makes a request that requires more than 50 milliseconds to process, the request is spread out over multiple sweeps so that no one sweep is impacted by more than 50 milliseconds.

Figure 2-3. System Communications Window Flow Chart

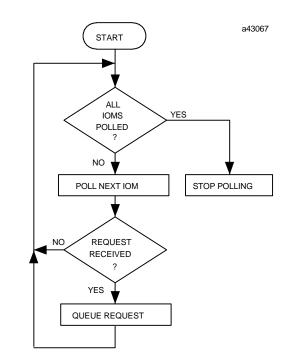

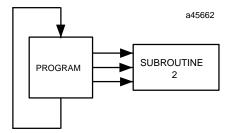

# PCM Communications with the PLC (Models 331 and Higher)

There is no way for intelligent option modules (IOM), such as the PCM, to interrupt the CPU when they need service. The CPU must poll each intelligent option module for service requests. This polling occurs asynchronously in the background during the sweep (see flow chart below).

When an intelligent option module is polled and sends the CPU a service request, the request is queued for processing during the system communications window.

Figure 2-4. PCM Communications with the PLC

## DSM Communications with the PLC

The DSM302 is an intelligent module operating asynchronously with the Series 90-30 CPU module. Data is exchanged between the CPU and the DSM automatically.